FPGA开发指南:逻辑设计篇

《FPGA开发指南:逻辑设计篇》一书是由田耘、胡彬合著的计算机类书籍,由人民邮电出版社于2008年出版发行。该书详细讲解了Xilinx ISE Design Suite 10.1软件的操作方法和它在逻辑设计、DSP开发、嵌入式设计和高速传输领域的应用。

FPGA开发指南:逻辑设计篇基本信息

| 书名 | FPGA开发指南 | 作者 | 田耘 胡彬 |

|---|---|---|---|

| ISBN | 9787115187369 | 出版社 | 人民邮电出版社 |

《XilinxISEDesignSuite10.xFPGA开发指南:逻辑设计篇》以XilinxFPGA逻辑开发流程为主线,以浅入深出、图文并茂的方式,全面、详细地介绍了Xilinx公司的终极开发套件ISEDesignSuite10.1中逻辑开发的操作方法,并精选了多个实际开发案例进行深入讲解。书中内容结合了作者多年的实际开发经验,具有很高的实践指导价值。

FPGA开发指南:逻辑设计篇造价信息

第1章 FPGA开发基础知识

1.1 可编程逻辑器件基础

1.1.1 可编程逻辑器件概述

1.1.2 可编程逻辑器件的发展历史

1.1.3 可编程逻辑器件开发工具

1.2 FPGA器件的基础知识

1.2.1 FPGA芯片的基本工作原理

1.2.2 Xilinx FPGA的基本架构

1.2.3 典型的FPGA开发流程

1.2.4 基于FPGA的SoC设计方法

1.2.5 FPGA芯片与设计的性能指标

1.3 本章小结

第2章 Xilinx FPGA资源简介

2.1 Xilinx最新FPGA

2.1.1 高端平台Virtex 5系列

2.1.2 中低端平台Spartan 3E系列

2.2 Xilinx主流芯片介绍

2.2.1 Xilinx FPGA芯片介绍

2.2.2 Xilinx PROM芯片介绍

2.2.3 Xilinx芯片的选型

2.3 Xilinx FPGA的开发资源

2.3.1 Xilinx FPGA在通信领域中的解决方案

2.3.2 Xilinx FPGA在汽车电子领域中的解决方案

2.3.3 Xilinx FPGA在工业/科学/医疗领域中的解决方案

2.3.4 Xilinx FPGA在宇航和国防领域中的解决方案

2.3.5 Xilinx FPGA在其他领域中的解决方案

2.4 Xilinx FPGA的电子文档资源

2.4.1 Xilinx官方文档分类

2.4.2 ISE软件自带文档

2.4.3 Xilinx 电子文档资源的搜索技巧

2.4.4 FPGA设计人员的进阶路线

2.5 Xilinx FPGA芯片管脚解读

2.5.1 FPGA芯片的封装形式

2.5.2 FPGA芯片的管脚介绍

2.5.3 FPGA芯片管脚的分配策略

2.6 本章小结

第3章 新一代开发工具 ISE Design Suite 10.1

3.1 ISE Design Suite 10.1简介

3.1.1 ISE Design Suite 10.1综述

3.1.2 ISE Design Suite 10.1的创新特性

3.2 ISE Design Suite 10.1主要组件

3.2.1 ISE Foundation

3.2.2 EDK开发工具

3.2.3 DSP工具

3.2.4 ChipScope Pro

3.2.5 PlanAhead

3.3 本章小结

第4章 ISE Foundation基本组件

4.1 ISE Foundation的介绍与安装

4.1.1 ISE Foundation简要介绍

4.1.2 ISE软件的安装

4.1.3 ISE软件的基本操作

4.1.4 ISE软件的开发操作流程

4.2 基于ISE的工程建立与设计输入

4.2.1 新建工程

4.2.2 HDL代码输入

4.2.3 状态机的输入与验证

4.2.4 原理图输入法

4.2.5 代码模板的使用

4.2.6 Xilinx IP Core的使用

4.3 基于ISE的仿真

4.3.1 基于波形测试法的仿真

4.3.2 基于HDL测试代码的仿真

4.4 基于ISE的综合与实现

4.4.1 基于Xilinx XST的综合

4.4.2 基于ISE的实现

4.4.3 基于目标和用户策略的设计方法

4.4.4 基于SmartXplorer/Xplorer 的实现技术

4.4.5 基于SmartCompile的设计保存技术

4.5 用户约束文件

4.5.1 约束文件的基本知识

4.5.2 UCF文件的语法说明

4.5.3 管脚和区域约束语法

4.5.4 时序约束语法

4.6 管脚和区域约束工具Floorplan Editor

4.6.1 Floorplan Editor功能简介

4.6.2 利用PACE完成管脚分配

4.6.3 使用Floorplan Editor完成管脚分配和区域约束

4.6.4 Floorplan Editor的其他功能

4.7 时序约束工具Constraints Editor

4.7.1 Constraints Editor功能简介

4.7.2 利用Constraints Editor添加时序约束

4.7.3 利用Constraints Editor添加分组约束

4.7.4 利用Constraints Editor添加专用约束

4.8 基于ISE的器件配置

4.8.1 FPGA配置电路

4.8.2 iMPACT参数设置

4.8.3 配置FPGA器件

4.8.4 配置PROM器件

4.9 本章小结

第5章 ISE Foundation高级组件

5.1 在线逻辑分析仪ChipScope Pro

5.1.1 ChipScope Pro工具简介

5.1.2 ChipScope Core Generator使用说明

5.1.3 ChipScope Core Inserter使用说明

5.1.4 ChipScope Core Analyzer使用说明

5.1.5 ChipScope Pro Serial I/O Toolkit使用说明

5.1.6 ChipScope Pro应用实例

5.2 平面布局规划器PlanAhead

5.2.1 PlanAhead 10.1的安装及新特性

5.2.2 PlanAhead设计流程

5.2.3 利用PinAhead进行I/O引脚规划

5.2.4 使用ExploreAhead优化实现结果

5.3 时序分析器Timing Analyzer

5.3.1 时序分析基础

5.3.2 Xilinx FPGA中的时钟资源

5.3.3 ISE时序分析器的软件操作

5.3.4 Timing Analyzer应用实例

5.4 布局规划器Floorplanner

5.4.1 Floorplanner简介

5.4.2 Floorplanner软件操作

5.4.3 Floorplanner应用实例

5.5 底层编辑器FPGA Editor

5.5.1 FPGA Editor简介

5.5.2 FPGA Editor软件操作

5.5.3 FPGA Editor应用实例

5.6 功耗分析工具XPower

5.6.1 功耗分析简介

5.6.2 XPower估计器

5.6.3 XPower分析器

5.6.4 低功耗设计技术

5.6.5 XPower分析器应用实例

5.7 本章小结

第6章 ISE与第三方软件

6.1 ModelSim仿真软件的使用

6.1.1 ModelSim仿真软件的安装

6.1.2 在ModelSim中指定Xilinx的仿真库

6.1.3 ModelSim的基本操作

6.1.4 ModelSim的高级操作

6.2 综合工具Synplify Pro

6.2.1 Synplify Pro综合软件的安装

6.2.2 Synplify Pro的使用

6.3 ISE与MATLAB的联合使用

6.3.1 利用MATLAB辅助FPGA的逻辑设计

6.3.2 利用MATLAB完成DSP系统开发

6.3.3 利用MATLAB自动生成滤波器代码

6.4 本章小结

第7章 FPGA底层单元与逻辑开发实例

7.1 FPGA底层单元开发

7.1.1 Xilinx全局时钟网络的使用

7.1.2 DCM模块的使用

7.1.3 Xilinx内嵌块存储器的使用

7.1.4 硬核乘加器DSP48的使用

7.2 FPGA常用IP Core使用实例

7.2.1 Cordic算法IP Core的使用

7.2.2 FFT算法IP Core的使用

7.2.3 FIR滤波器IP Core的使用

7.3 开发实例-LMS算法的Verilog实现

7.3.1 LMS算法的原理

7.3.2 LMS算法的MATLAB实现

7.3.3 LMS算法的FPGA实现

7.3.4 LMS算法的软件调试

7.4 本章小结

附录 Verilog HDL语言基础

参考文献

书 名: FPGA开发指南:逻辑设计篇

作 者:田耘 胡彬

出版社: 人民邮电出版社

出版时间: 2008

ISBN: 9787115187369

开本: 16

定价: 59.00 元

FPGA开发指南:逻辑设计篇常见问题

-

74138是二进制译码器,3个数据输入、8个数据输出、3个芯片选择输入端子。芯片有效时(片选),输出端子有效的一位就是输入值的译码值,如:输入001,Y1=0,其余输出全为1,138是低电平有效。13...

-

数字电路与逻辑设计是计算机专业和电子信息类专业的一门硬件基础课。数字电路与逻辑设计:主要内容包括数字逻辑电路基础知识、逻辑门、逻辑代数与逻辑函数、组合逻辑电路、触发器、时序逻辑电路、半导体存储器和可编...

-

做的太久,需要活动一下。

《XilinxISEDesignSuite10.xFPGA开发指南:逻辑设计篇》针对性较强,可满足实际工程开发的需求。《XilinxISEDesignSuite10.xFPGA开发指南:逻辑设计篇》可作为电子和通信工程师的实用工具书,还可作为高等院校通信工程、电子工程、计算机以及微电子与集成电路等相关专业的高年级本科生以及研究生的教材和学习参考书。

FPGA开发指南:逻辑设计篇文献

Verilog实现的基于FPGA的五层楼电梯运行控制逻辑设计

Verilog实现的基于FPGA的五层楼电梯运行控制逻辑设计

五层楼电梯运行控制逻辑设计 摘要:电梯是高层建筑不可缺少的运输工具,用于垂直运送乘客和货物,传统的电梯控制系 统主要采用继电器,接触器进行控制,其缺点是触点多,故障率高、可靠性差、维修工作量 大等,本设计根据电梯自动控制的要求利用 Verilog语言编写并完成系统设计, 在利用软件仿 真之后,下载到了 FPGA上进行硬件仿真。 FPGA(Field-Programmable Gate Array),即现 场可编程门阵列,它是在 PAL、GAL、CPLD 等可编程器件的基础上进一步发展的产物。它 是作为专用集成电路 (ASIC)领域中的一种半定制电路而出现的, 既解决了定制电路的不足, 又克服了之前的可编程器件门电路数有限及速度上的缺点。 关键词:电梯控制 FPGA Verilog 软件设计 硬件设计 在当今社会,随着城市建设的不断发展,高层建筑的不断增多,电梯作为高层建筑中垂 直运行的交通

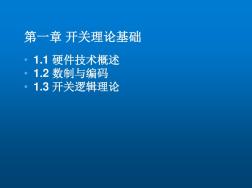

计算机逻辑设计第1章开关理论基础

计算机逻辑设计第1章开关理论基础

计算机逻辑设计第1章开关理论基础

在众多汽车电子系统开发领域中,赛车一直是FPGA大显身手的场所。在汽车ECU领域,FPGA可协助提升灵活性、性能和可靠性。各大涉及赛车业务的机构,如先进引擎研究有限公司(AER,AdvancedEngineResearchLtd)属下的电子设计部LifeRacing,已开始在其ECU设计中引入Actel以Flash为基础ProASICPlus的FPGA器件。有竞争力的赛车ECU需要采用复杂的调节算法,专为每个独立的控制器而优化,以管理引擎的定时功能。使用传统的解决方案即标准定时处理单元(TPU)控制器,这个关键软件会随着应用要求的改变,需要进行重大的修改。然而,借助基于Flash的FPGA的系统内可重编程功能(ISP),设计人员可以利用单芯片的上电运行FPGA器件取代以往的TPU控制器,从而缩短软件开发时间、减少调试需求和加速产品的整体上市时间。

在ECU中,一般FPGA的主要功能是从机轴触轮信号中提取引擎的位置信息。FPGA会根据抽象的机轴角度发出CPU中断信号,而非传统设计应用的触轮齿位,因而提高了灵活性和精度。ECU通常会将燃料添加和点火动作编为定时的调度事件,并以调度代码执行时间的引擎工作状况为基础。在事件发生前改变引擎工作状态会引起角度误差,而调度代码往往与当前引擎的机轴触轮轮齿式样密切相关。FPGA能令调度代码不受信号式样影响,还能通过监测引擎工作状况来进行事件调度和持续调节,直至事件发生。此举能提升代码效率和灵活性,同时改善动态状况下的控制精度。而且,基于Flash的FPGA(如Actel的ProASICPlus)的上电运行功能,能助设计人员除去传统需要用来阻止燃料注射驱动器或点火线圈驱动器在上电期间启动的附加元件。

LifeRacing专有的ECU设计F88便成功地应用于2003年度SuperfundWorldSeries的第一轮赛事中-这是进入一级方程式大赛(Formula1)的重要踏脚石。

目前,商用道路车辆制造商也在考虑采用LifeRacing的ECU。这个控制单元具有高度灵活性,最适用于原型制造和研发环境,能应付各式不同的引擎设置。FPGA正获得广泛接纳,用于新一代汽车电子的设计方案中。在选择FPGA的过程中深入了解各种技术的独特性能,汽车设计人员便能从最有前景的技术中获益,而不会影响业界在制造高可靠性和成本效益汽车方面的美誉。

汽车电子设计人员通过使用具有扩展温度范围的FPGA技术,能够显著提高应对多种故障的能力。虽然许多元件供应商采用预防性的设计技术及限定方法来模拟和仿真环境影响,但是某些FPGA构架在承受扩展温度范围方面仍然具有先天优势。举例说,Actel以反熔丝为基础的汽车器件能承受业界最高的结点温度(+150℃),为设计人员的高可靠性系统带来更大的性能冗余。

在高温下工作的能力不仅有利于抵御故障。由于汽车电子应用在空间和成本上都没有余地来加设风扇和散热装置,因此器件必须在没有外部散热装置的情况下仍能提供所需的性能。

极端的环境往往会导致与FPGA组装和封装相关的故障模式,而与装置本身无关。所以在汽车电子系统的各个层面预留规格余地非常重要。FPGA供货商如Xilinx和Actel等提供的产品具有较宽的军用温度范围,能够更好地定义热膨胀系数,避免热应力的影响。

即使在正常的温度和电压下工作,在FPGA的栅极氧化膜上反复施加电压应力最终也会使器件内的电介质绝缘层发生击穿。这种随使用时间累计而产生的击穿现象称为"时间相关绝缘击穿"(TDDB)。加上深亚微米技术的应用,会增加这类故障在现场发生的风险。

过去汽车电子产品的开发周期是漫长的,而现在许多汽车制造商现正致力于在更短的时间内,装备消费者所需的新一代汽车。诸如GPS导航系统和DVD播放机等设备的产品生命周期相对较短,因此,产品推向市场的速度非常重要。今天,采用ASIC可能会使开发周期增加30周,加上掩模成本大幅攀升,使得开支和风险也进一步提高。

与此同时,因为当今的汽车引入了许多标准和技术,使ASIC的应用缺乏灵活性,从而增加其被废弃和延迟应用的风险。消费者还要求享有各种功能选项,使得汽车厂商必需以一套元件组合为基础,再根据不同需求进行配置。为了快速实现这些高度集成和不断变化的系统,能够使产品快速推向市场的FPGA为汽车厂商带来了所需的灵活性,可在现场进行系统硬件升级,而毋须执行昂贵的返工工程和部件更换。所以,FPGA现已应用于汽车电子中,范畴从设计验证到制造和服务。随着汽车内的空间日益宝贵,可编程逻辑能在小型单芯片方案上集成许多不同功能的特性也显得极具吸引。

- 相关百科

- 相关知识

- 相关专栏

- 装表接电与内线安装

- XML技术教程

- 生产系统建模与仿真

- 高性能CUDA应用设计与开发

- 2013年韩国国际电力展Global Electric Power Tech

- 开发自己的搜索引擎---Lucene+Heritrix(第2版)

- 四极滤质器

- 国标螺旋钢管

- 网络数据库技术及应用

- SQLServer数据库设计与管理

- 迎吉花苑

- 卫生设备故障50例

- 流量及分析仪表

- AutoCAD2012室内设计高手速成

- 恒仪门轴

- 不锈钢箱变

- 中、小跨径钢筋混凝土拱桥现浇支架(拱架)设计指南

- 招投标制在农业综合开发工程建设中的实践与对策建议

- 云南加快澜沧江下游水电开发 顺利实施向泰国送电

- 亚洲开发银行贷款项目工程投标

- 在房地产开发中如何运用法律防范可能发生的违约行为

- 以工作过程为导向的市政管道工程施工课程开发与实践

- 在改革创新中奋进的国电新疆吉林台水电开发有限公司

- 中国石化炼化企业VOCs综合治理技术指南(试行)

- 招投标制在农业综合开发工程建设中的实践与对策

- 中国水电资源在开发和利用中存在的问题及其解决方法

- 中国城市土地开发模式的演进及其对房地产市场的影响

- 掌上电脑配合GPS的道路勘测设计系统的开发及应用

- 状态优化的I~2C总线主控制器的FPGA设计

- 中国水电能源开发利用

- 依靠科技进步发挥优良传统开发西藏水电造福西藏人民

- 憎水炉砟粉煤灰水泥防水保温隔热屋面板的研制与开发