PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)

PCI是Peripheral Component Interconnect(外设部件互连标准)的缩写,它是目前个人电脑中使用最为广泛的接口,几乎所有的主板产品上都带有这种插槽。PCI插槽也是主板带有最多数量的插槽类型,在目前流行的台式机主板上,ATX结构的主板一般带有5~6个PCI插槽,而小一点的MATX主板也都带有2~3个PCI插槽,可见其应用的广泛性。

- PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)总线设备

- PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)造价信息

- PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)主要性能

- PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)PCI定义

- PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)常见问题

- PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)PCI总线结构

- PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)总线特点

- PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)总线信号

- PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)文献

- PCI总线:PCI概述

- PCI总线规格简介

- PCI总线总线特点

PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)图片

PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)基本信息

| 中文名称 | PCI总线 | 外文名称 | Peripheral Component Interconnect |

|---|---|---|---|

| 释义 | 个人电脑中使用最为广泛的接 | 规范时间 | 1992年 |

在PCI总线中有三类设备,PCI主设备、PCI从设备和桥设备。其中PCI从设备只能被动地接收来自HOST主桥,或者其他PCI设备的读写请求;而PCI主设备可以通过总线仲裁获得PCI总线的使用权,主动地向其他PCI设备或者主存储器发起存储器读写请求。而桥设备的主要作用是管理下游的PCI总线,并转发上下游总线之间的总线事务。

一个PCI设备可以即是主设备也是从设备,但是在同一个时刻,这个PCI设备或者为主设备或者为从设备。PCI总线规范将PCI主从设备统称为PCI Agent设备。在处理器系统中常见的PCI网卡、显卡、声卡等设备都属于PCI Agent设备。

在PCI总线中,HOST主桥是一个特殊的PCI设备,该设备可以获取PCI总线的控制权访问PCI设备,也可以被PCI设备访问。但是HOST主桥并不是PCI设备。PCI规范也没有规定如何设计HOST主桥。

在PCI总线中,还有一类特殊的设备,即桥设备。桥设备包括PCI桥、PCI-to-(E)ISA桥和PCI-to-Cardbus桥。PCI桥的存在使PCI总线极具扩展性,处理器系统可以使用PCI桥进一步扩展PCI总线。

PCI桥的出现使得采用PCI总线进行大规模系统互连成为可能。但是在目前已经实现的大规模处理器系统中,并没有使用PCI总线进行处理器系统与处理器系统之间的大规模互连。因为PCI总线是一个以HOST主桥为根的树型结构,使用主从架构,因而不易实现多处理器系统间的对等互连。

即便如此PCI桥仍然是PCI总线规范的精华所在,掌握PCI桥是深入理解PCI体系结构的基础。PCI桥可以连接两条PCI总线,上游PCI总线和下游PCI总线,这两个PCI总线属于同一个PCI总线域,使用PCI桥扩展的所有PCI总线都同属于一个PCI总线域。

其中对PCI设备配置空间的访问可以从上游总线转发到下游总线,而数据传送可以双方向进行。在PCI总线中,还存在一种非透明PCI桥,该桥片不是PCI总线规范定义的标准桥片,但是适用于某些特殊应用。

PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)造价信息

(1)传输速率高最大数据传输率为132MB/s,当数据宽度升级到64位,数据传输率可达264MB/s。这是其他总线难以比拟的。它大大缓解了数据I/O瓶颈,使高性能CPU的功能得以充分发挥,适应高速设备数据传输的需要。

(2)多总线共存采用PCI总线可在一个系统中让多种总线共存,容纳不同速度的设备一起工作。通过HOST-PCI桥接组件芯片,使CPU总线和PCI总线桥接;通过PCI-ISA/EISA桥接组件芯片,将PCI总线与ISA/EISA总线桥接,构成一个分层次的多总线系统。高速设备从ISA/EISA总线卸下来,移到PCI总线上,低速设备仍可挂在ISA/EISA总线上,继承原有资源,扩大了系统的兼容性。

(3)独立于CPU PCI总线不依附于某一具体处理器,即PCI总线支持多种处理器及将来发展的新处理器,在更改处理器品种时,更换相应的桥接组件即可。

(4)自动识别与配置外设 用户使用方便。

(5)并行操作能力。

PCI (Peripheral Component Interconnect)总线是一种高性能局部总线,是为了满足外设间以及外设与主机间高速数据传输而提出来的。在数字图形、图像和语音处理,以及高速实时数据采集与处理等对数据传输率要求较高的应用中,采用PCI总线来进行数据传输,可以解决原有的标准总线数据传输率低带来的瓶颈问题。

PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)PCI定义

PCI总线特点

PCI 总线结构图

PCI即Peripheral Component Interconnect,中文意思是"外围器件互联",是由PCISIG (PCI Special Interest Group)推出的一种局部并行总线标准。PCI总线是由ISA(Industy Standard Architecture)总线发展而来的,ISA并行总线有8位和16位两种模式,时钟频率为8MHz,工作频率为33MHz/66MHz。是一种同步的独立于处理器的32位或64位局部总线。从结构上看,PCI是在CPU的供应商和原来的系统总线之间插入的一级总线,具体由一个桥接电路实现对这一层的管理,并实现上下之间的接口以协调数据的传送。从1992年创立规范到如今,PCI总线已成为了计算机的一种标准总线。已成为局部总线的新标准,广泛用于当前高档微机、工作站,以及便携式微机。主要用于连接显示卡、网卡、声卡。PCI总线是32位同步复用总线。其地址和数据线引脚是AD31~AD0。PCI的工作频率为33MHz。

PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)常见问题

-

pci调制解调器就是内置的调制解调器。内置式调制解调器其实就是一块计算机的扩展卡,插入计算机内的一个扩展槽即可使用,无需占用计算机的串行端口。连线相当简单,把电话线接头插入卡上的“Line”插口,卡上...

-

软盘驱动器和软盘属于外部设备。外部设备,简称“外设”。计算机系统中输入、输出设备(包括外存储器)的统称。对数据和信息起着传输、转送和存储的作用。是计算机系统中的重要组成部分。

PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)PCI总线结构

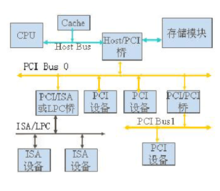

PCI总线是一种树型结构,并且独立于CPU总线,可以和CPU总线并行操作。PCI总线上可以挂接PCI设备和PCI桥片,PCI总线上只允许有一个PCI主设备,其他的均为PCI 从设备,而且读写操作只能在主从设备之间进行,从设备之间的数据交换需要通过主设备中转。PCI总线结构如下图所示。

在处理器系统中,含有PCI总线和PCI总线树这两个概念。这两个概念并不相同,在一颗PCI总线树中可能具有多条PCI总线,而具有血缘关系的PCI总线组成一颗PCI总线树。PCI总线由HOST主桥或者PCI桥管理,用来连接各类设备,如声卡、网卡和IDE接口卡等。在一个处理器系统中,可以通过PCI桥扩展PCI总线,并形成具有血缘关系的多级PCI总线,从而形成PCI总线树型结构。在处理器系统中有几个HOST主桥,就有几颗这样的PCI总线树,而每一颗PCI总线树都与一个PCI总线域对应。

与HOST主桥直接连接的PCI总线通常被命名为PCI总线0。考虑到在一个处理器系统中可能有多个主桥。

PCI总线取代了早先的ISA总线。当然与在PCI总线后面出现专门用于显卡的AGP总线,与现在的PCI Express总线相比,功能没有那么强大,但是PCI能从1992用到现在,说明他有许多优点,比如即插即用(Plug and Play)、中断共享等。在这里我们对PCI总线做一个深入的介绍。

从数据宽度上看,PCI总线有32bit、64bit之分;从总线速度上分,有33MHz、66MHz两种。目前流行的是32bit @ 33MHz,而64bit系统正在普及中。改良的PCI系统,PCI-X,最高可以达到64bit @ 133MHz,这样就可以得到超过1GB/s的数据传输速率。如果没有特殊说明,以下的讨论以32bit @ 33MHz为例。

不同于ISA总线,PCI总线的地址总线与数据总线是分时复用的。这样做的好处是,一方面可以节省接插件的管脚数,另一方面便于实现突发数据传输。在做数据传输时,由一个PCI设备做发起者(主控,Initiator或Master),而另一个PCI设备做目标(从设备,Target或Slave)。总线上的所有时序的产生与控制,都由Master来发起。PCI总线在同一时刻只能供一对设备完成传输,这就要求有一个仲裁机构(Arbiter),来决定在谁有权力拿到总线的主控权。

当PCI总线进行操作时,发起者(Master)先置REQ#,当得到仲裁器(Arbiter)的许可时(GNT#),会将FRAME#置低,并在AD总线上放置Slave地址,同时C/BE#放置命令信号,说明接下来的传输类型。所有PCI总线上设备都需对此地址译码,被选中的设备要置DEVSEL#以声明自己被选中。然后当IRDY#与TRDY#都置低时,可以传输数据。当Master数据传输结束前,将FRAME#置高以标明只剩最后一组数据要传输,并在传完数据后放开IRDY#以释放总线控制权。

这里我们可以看出,PCI总线的传输是很高效的,发出一组地址后,理想状态下可以连续发数据,峰值速率为132MB/s。实际上,目前流行的33M@32bit北桥芯片一般可以做到100MB/s的连续传输。

PCI总线特点

(1)传输速率高最大数据传输率为132MB/s,当数据宽度升级到64位,数据传输率可达264MB/s。这是其他总线难以比拟的。它大大缓解了数据I/O瓶颈,使高性能CPU的功能得以充分发挥,适应高速设备数据传输的需要。

(2)多总线共存采用PCI总线可在一个系统中让多种总线共存,容纳不同速度的设备一起工作。通过HOST-PCI桥接组件芯片,使CPU总线和PCI总线桥接;通过PCI-ISA/EISA桥接组件芯片,将PCI总线与ISA/EISA总线桥接,构成一个分层次的多总线系统。高速设备从ISA/EISA总线卸下来,移到PCI总线上,低速设备仍可挂在ISA/EISA总线上,继承原有资源,扩大了系统的兼容性。

(3)独立于CPU PCI总线不依附于某一具体处理器,即PCI总线支持多种处理器及将来发展的新处理器,在更改处理器品种时,更换相应的桥接组件即可。

(4)自动识别与配置外设 用户使用方便。

(5)并行操作能力。

PCI总线的主要性能

(1)总线时钟频率33.3MHz/66.6MHz。

(2)总线宽度32位/64位。

(3)最大数据传输率132MB/s(264MB/s)。

(4)支持64位寻址。

(5)适应5V和3.3V电源环境。

即插即用的实现

所谓即插即用,是指当板卡插入系统时,系统会自动对板卡所需资源进行分配,如基地址、中断号等,并自动寻找相应的驱动程序。而不象旧的ISA板卡,需要进行复杂的手动配置。

实际的实现远比说起来要复杂。在PCI板卡中,有一组寄存器,叫"配置空间"(Configuration Space),用来存放基地址与内存地址,以及中断等信息。

以内存地址为例。当上电时,板卡从ROM里读取固定的值放到寄存器中,对应内存的地方放置的是需要分配的内存字节数等信息。操作系统要跟据这个信息分配内存,并在分配成功后把相应的寄存器中填入内存的起始地址。这样就不必手工设置开关来分配内存或基地址了。对于中断的分配也与此类似。

中断共享的实现

ISA卡的一个重要局限在于中断是独占的,而我们知道计算机的中断号只有16个,系统又用掉了一些,这样当有多块ISA卡要用中断时就会有问题了。

PCI总线的中断共享由硬件与软件两部分组成。

硬件上,采用电平触发的办法:中断信号在系统一侧用电阻接高,而要产生中断的板卡上利用三极管的集电极将信号拉低。这样不管有几块板产生中断,中断信号都是低;而只有当所有板卡的中断都得到处理后,中断信号才会恢复高电平。

软件上,采用中断链的方法:假设系统启动时,发现板卡A用了中断7,就会将中断7对应的内存区指向A卡对应的中断服务程序入口ISR_A;然后系统发现板卡B也用中断7,这时就会将中断7对应的内存区指向ISR_B,同时将ISR_B的结束指向ISR_A。以此类推,就会形成一个中断链。而当有中断发生时,系统跳转到中断7对应的内存,也就是ISR_B。ISR_B就要检查是不是B卡的中断,如果是,要处理,并将板卡上的拉低电路放开;如果不是,则呼叫ISR_A。这样就完成了中断的共享。

通过以上讨论,我们不难看出,PCI总线有着极大的的优势。而近年来的市场情况也证实了这一点。

PCI总线是一种同步的独立于处理器的32位或64位局部总线,最高工作频率为33MHz,峰值速度在32位时为132MB/s,64位时为264MB/s,总线规范由PCISIG发布。ISA总线相比,PCI总线和有如下显著的特点:

(1)高速性

PCI局部总线以33MHz的时钟频率操作,采用32位数据总线,数据传输速率可高达132MB/s,远超过以往各种总线。而早在1995年6月推出的PCI总线规范2。l已定义了64位、66MHz的PCI总线标准。因此PCI总线完全可为未来的计算机提供更高的数据传送率。另外,PCI总线的主设备(Master)可与微机内存直接交换数据,而不必经过微机CPU中转,也提高了数据传送的效率。

(2)即插即用性

目前随着计算机技术的发展,微机中留给用户使用的硬件资源越来越少,也越来越含糊不清。在使用ISA板卡时,有两个问题需要解决:一是在同一台微机上使用多个不同厂家、不同型号的板卡时,板卡之间可能会有硬件资源上的冲突;二是板卡所占用的硬件资源可能会与系统硬件资源(如声卡、网卡等)相冲突。而PCI板卡的硬件资源则是由微机根据其各自的要求统一分配,决不会有任何的冲突问题。因此,作为PCI板卡的设计者,不必关心微机的哪些资源可用,哪些资源不可用,也不必关心板卡之间是否会有冲突。因此,即使不

考虑PCI总线的高速性,单凭其即插即用性,就比ISA总线优越了许多。

(3)可靠性

PCI独立于处理器的结构,形成一种独特的中间缓冲器设计方式,将中央处理器子系统与外围设备分开。这样用户可以随意增添外围设备,以扩充电脑系统而不必担心在不同时钟频率下会导致性能的下降。与原先微机常用的ISA总线相比,PCI总线增加了奇偶校验错(PERR)、系统错(SERR)、从设备结束(STOP)等控制信号及超时处理等可靠性措施,使数据传输的可靠性大为增加。

(4)复杂性

PCI总线强大的功能大大增加了硬件设计和软件开发的实现难度。硬件上要采用大容量、高速度的CPLD或FPGA芯片来实现PCI总线复杂的功能。软件上则要根据所用的操作系统,用软件工具编制支持即插即用功能酶设备驱动程序。

(5)自动配置

PCI总线规范规定PCI插卡可以自动配置。PCI定义了3种地址空间:存储器空间,输入输出空间和配置空间,每个PCI设备中都有256字节的配置空间用来存放自动配置信息,当PCI插卡插入系统,BIOS将根据读到的有关该卡的信息,结合系统的实际情况为插卡分配存储地址、中断和某些定时信息。

(6)共享中断

PCI总线是采用低电平有效方式,多个中断可以共享一条中断线,而ISA总线是边沿触发方式。

(7)扩展性好

如果需要把许多设备连接到PCI总线上,而总线驱动能力不足时,可以采用多级PCI总线,这些总线上均可以并发工作,每个总线上均可挂接若干设备。因此PCI总线结构的扩展性是非常好的。由于PCI的设计是要辅助现有的扩展总线标准,因此与ISA,EISA及MCA总线完全兼容。

(8)多路复用

在PCI总线中为了优化设计采用了地址线和数据线共用一组物理线路,即多路复用。PCI接插件尺寸小,又采用了多路复用技术,减少了元件和管脚个数,提高了效率。

(9)严格规范

PCI总线对协议、时序、电气性能、机械性能等指标都有严格的规定,保证了PCI的可靠性和兼容性。由于PCI总线规范十分复杂,其接口的实现就有较高的技术难度。

PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)总线信号

PCI总线信号定义示意图

PCI总线标准所定义的信号线通常分成必需的和可选的两大类。其信号线总数为120条(包括电源、地、保留引脚等)。其中,必需信号线:主控设备49条,目标设备47条。可选信号线:51条(主要用于64位扩展、中断请求、高速缓存支持等)。主设备是指取得了总线控制权的设备,而被主设备选中以进行数据交换的设备称为从设备或目标设备。作为主设备需要49条信号线,若作为目标设备,则需要47条信号线,可选的信号线有51条。利用这些信号线便可以传输数据、地址,实现接口控制、仲裁及系统的功能。PCI局部总线信号如下所示。下面按功能分组进行说明:

1)系统信号CLK IN:系统时钟信号,为所有PCI传输提供时序,对于所有的PCI设备都是输入信号。其频率最高可达33MHz/66MHz,这一频率也称为PCI的工作频率。 RST# IN:复位信号。用来迫使所有PCI专用的寄存器、定序器和信号转为初始状态。

2).地址和数据信号 AD[31::00]T/S:地址、数据复用的信号。PCI总线上地址和数据的传输,必需在FRAME#有效期间进行。当FRAME#有效时的第1个时钟,AD[31::00]上的信号为地址信号,称地址期;当IRDY#和TRDY#同时有效时,AD[31::00]上的信号为数据信号,称数据期。一个PCI总线传输周期包含一个地址期和接着的一个或多个数据期。 C/BE[3::0]# T/S:总线命令和字节允许复用信号。在地址期,这4条线上传输的时总线命令;在数据期,它们传输的时字节允许信号,用来指定在数据期,AD[31::00]线上4个数据字节中哪些字节为有效数据,以进行传输。 PAR T/S:奇偶校验信号。它通过AD[31::00]和C/BE[3::0]进行奇偶校验。主设备为地址周期和写数据周期驱动PAR,从设备为读数据周期驱动PAR。

3).接口控制信号 FRAME# S/T/S:帧周期信号,由主设备驱动。表示一次总线传输的开始和持续时间。当FRAME#有效时,预示总线传输的开始;在其有效期间,先传地址,后传数据;当FRAME#撤消时,预示总线传输结束,并在IRDY#有效时进行最后一个数据期的数据传送。 IRDY# S/T/S:主设备准备好信号。IRDY#要与TRDY#联合使用,当二者同时有效时,数据方能传输,否则,即为未准备好二进入等待周期。在写周期,该信号有效时,表示数据已由主设备提交到AD[31::00]线上;在读周期,该信号有效时,表示主设备已做好接收数据的准备。 TRDY# S/T/S:从设备(被选中的设备)准备好信号。同样TRDY#要与IRDY#联合使用,只有二者同时有效,数据才能传输。 STOP# S/T/S:从设备要求主设备停止当前的数据传送的信号。显然,该信号应由从设备发出。LOCK# S/T/S:锁定信号。当对一个设备进行可能需要多个总线传输周期才能完成的操作时,使用锁定信号LOCK#,进行独占性访问。例如,某一设备带有自己的存储器,那么它必需能进行锁定,以便实现对该存储器的完全独占性访问。也就是说,对此设备的操作是排它性的。IDSEL IN:初始化设备选择信号。在参数配置读/写传输期间,用作片选信号。 DEVSEL# S/T/S:设备选择信号。该信号由从设备在识别处地址时发出,当它有效时,说明总线上有某处的某一设备已被选中,并作为当前访问的从设备。

4).仲裁信号(只用于总线主控器) REQ# T/S:总线占用请求信号。该信号有效表明驱动它的设备要求使用总线。它是一个点到点的信号线,任何主设备都有它自己的REQ#信号。 GNT# T/S:总线占用允许信号。该信号有效,表示申请占用总线的设备的请求已获得比准。

5).错误报告信号 PERR# S/T/S:数据奇偶校验错误报告信号。一个设备只有在响应设备选择信号(DEVSEL#)和完成数据期之后,才能报告一个PERR#。SERR# O/D:系统错误报告信号。用做报告地址奇偶错、特殊命令序列中的数据奇偶错,以及其他可能引起灾难性后果的系统错误。它可由任何设备发出。

6).中断信号 在PCI总线中,中断是可选项,不一定必须具有。INTA# O/D:用于请求中断。INTB# O/D、INTC# O/D、INTD# O/D:用于请求中断,仅对多功能设备有意义。所谓的多功能设备是指:将几个相互独立的功能集中在一个设备中。各功能与中断线之间的连接是任意的,没有任何附加限制。

7.)其他可选信号 (1)高速缓存支持信号:SBO# IN/OUT、SDONE IN/OUT (2)64位总线扩展信号:REQ64# S/T/S、ACK65# S/T/S、AD[63::32]T/S、C/BE[7::4]#T/S、PAR64 T/S。 (3)测试访问端口/边界扫描信号:TCK IN、TDI IN、TDO OUT、TMS IN、TRST# IN。

PCI总线:PCI(PeripheralComponentInterconnect:外部设备互连)文献

基于Compact PCI总线的CAN总线扩展模块设计

基于Compact PCI总线的CAN总线扩展模块设计

介绍了PCI桥接口芯片PCI9030和CAN接口芯片SJA1000,给出了基于CPCI总线的CAN总线扩展模块软硬件的设计方案及实现方法。

基于Compact PCI总线的数字隔离I/O模块的实现

基于Compact PCI总线的数字隔离I/O模块的实现

本文结合自主研发的Compact PCI总线数字隔离I/O模块,介绍了模块的硬件和驱动解决方案,重点说明了模块与Compact PCI总线的接口部分设计、模块电气隔离的设计、模块WinDriver驱动程序的开发。

PCI总线: PCI(Peripheral Component Interconnect:外部设备互连)是由SIG集团推出的总线结构。它具有132 MB/S的数据传输率及很强的带负载能力,可适用于多种硬件平台,同时兼容ISA、EISA总线。

从1992年创立规范到如今,PCI总线已成为了计算机的一种标准总线。由PCI总线构成的标准系统结构如图一所示。

PCI总线取代了早先的ISA总线。当然与在PCI总线后面出现专门用于显卡的AGP总线,与现在的PCI Express总线相比,功能没有那么强大,但是PCI能从1992用到现在,说明他有许多优点,比如即插即用(Plug and Play)、中断共享等。在这里我们对PCI总线做一个深入的介绍。

从数据宽度上看,PCI总线有32bit、64bit之分;从总线速度上分,有33MHz、66MHz两种。目前流行的是32bit @ 33MHz,而64bit系统正在普及中。改良的PCI系统,PCI-X,最高可以达到64bit @ 133MHz,这样就可以得到超过1GB/s的数据传输速率。如果没有特殊说明,以下的讨论以32bit @ 33MHz为例。

一、基本概念

不同于ISA总线,PCI总线的地址总线与数据总线是分时复用的。这样做的好处是,一方面可以节省接插件的管脚数,另一方面便于实现突发数据传输。在做数据传输时,由一个PCI设备做发起者(主控,Initiator或Master),而另一个PCI设备做目标(从设备,Target或Slave)。总线上的所有时序的产生与控制,都由Master来发起。PCI总线在同一时刻只能供一对设备完成传输,这就要求有一个仲裁机构(Arbiter),来决定在谁有权力拿到总线的主控权。

当PCI总线进行操作时,发起者(Master)先置REQ#,当得到仲裁器(Arbiter)的许可时(GNT#),会将FRAME#置低,并在AD总线上放置Slave地址,同时C/BE#放置命令信号,说明接下来的传输类型。所有PCI总线上设备都需对此地址译码,被选中的设备要置DEVSEL#以声明自己被选中。然后当IRDY#与TRDY#都置低时,可以传输数据。当Master数据传输结束前,将FRAME#置高以标明只剩最后一组数据要传输,并在传完数据后放开IRDY#以释放总线控制权。

这里我们可以看出,PCI总线的传输是很高效的,发出一组地址后,理想状态下可以连续发数据,峰值速率为132MB/s。实际上,目前流行的33M@32bit北桥芯片一般可以做到100MB/s的连续传输。

二、即插即用的实现

所谓即插即用,是指当板卡插入系统时,系统会自动对板卡所需资源进行分配,如基地址、中断号等,并自动寻找相应的驱动程序。而不象旧的ISA板卡,需要进行复杂的手动配置。

实际的实现远比说起来要复杂。在PCI板卡中,有一组寄存器,叫"配置空间"(Configuration Space),用来存放基地址与内存地址,以及中断等信息。

以内存地址为例。当上电时,板卡从ROM里读取固定的值放到寄存器中,对应内存的地方放置的是需要分配的内存字节数等信息。操作系统要跟据这个信息分配内存,并在分配成功后把相应的寄存器中填入内存的起始地址。这样就不必手工设置开关来分配内存或基地址了。对于中断的分配也与此类似。

三、中断共享的实现

ISA卡的一个重要局限在于中断是独占的,而我们知道计算机的中断号只有16个,系统又用掉了一些,这样当有多块ISA卡要用中断时就会有问题了。

PCI总线的中断共享由硬件与软件两部分组成。

硬件上,采用电平触发的办法:中断信号在系统一侧用电阻接高,而要产生中断的板卡上利用三极管的集电极将信号拉低。这样不管有几块板产生中断,中断信号都是低;而只有当所有板卡的中断都得到处理后,中断信号才会恢复高电平。

软件上,采用中断链的方法:假设系统启动时,发现板卡A用了中断7,就会将中断7对应的内存区指向A卡对应的中断服务程序入口ISR_A;然后系统发现板卡B也用中断7,这时就会将中断7对应的内存区指向ISR_B,同时将ISR_B的结束指向ISR_A。以此类推,就会形成一个中断链。而当有中断发生时,系统跳转到中断7对应的内存,也就是ISR_B。ISR_B就要检查是不是B卡的中断,如果是,要处理,并将板卡上的拉低电路放开;如果不是,则呼叫ISR_A。这样就完成了中断的共享。

通过以上讨论,我们不难看出,PCI总线有着极大的的优势。而近年来的市场情况也证实了这一点。

PCI总线是一种同步的独立于处理器的32位或64位局部总线,最高工作频率为33MHz,峰值速度在32位时为132MB/s,64位时为264MB/s,总线规范由PCISIG发布。ISA总线相比,PCI总线和有如下显著的特点:

①高速性

PCI局部总线以33MHz的时钟频率操作,采用32位数据总线,数据传输速率可高达132MB/s,远超过以往各种总线。而早在1995年6月推出的PCI总线规范2。l已定义了64位、66MHz的PCI总线标准。因此PCI总线完全可为未来的计算机提供更高的数据传送率。另外,PCI总线的主设备(Master)可与微机内存直接交换数据,而不必经过微机CPU中转,也提高了数据传送的效率。

②即插即用性

目前随着计算机技术的发展,微机中留给用户使用的硬件资源越来越少,也越来越含糊不清。在使用ISA板卡时,有两个问题需要解决:一是在同一台微机上使用多个不同厂家、不同型号的板卡时,板卡之间可能会有硬件资源上的冲突;二是板卡所占用的硬件资源可能会与系统硬件资源(如声卡、网卡等)相冲突。而PCI板卡的硬件资源则是由微机根据其各自的要求统一分配,决不会有任何的冲突问题。因此,作为PCI板卡的设计者,不必关心微机的哪些资源可用,哪些资源不可用,也不必关心板卡之间是否会有冲突。因此,即使不

考虑PCI总线的高速性,单凭其即插即用性,就比ISA总线优越了许多。

③可靠性

PCI独立于处理器的结构,形成一种独特的中间缓冲器设计方式,将中央处理器子系统与外围设备分开。这样用户可以随意增添外围设备,以扩充电脑系统而不必担心在不同时钟频率下会导致性能的下降。与原先微机常用的ISA总线相比,PCI总线增加了奇偶校验错(PERR)、系统错(SERR)、从设备结束(STOP)等控制信号及超时处理等可靠性措施,使数据传输的可靠性大为增加。

④复杂性

PCI总线强大的功能大大增加了硬件设计和软件开发的实现难度。硬件上要采用大容量、高速度的CPLD或FPGA芯片来实现PCI总线复杂的功能。软件上则要根据所用的操作系统,用软件工具编制支持即插即用功能酶设备驱动程序。

⑤自动配置

PCI总线规范规定PCI插卡可以自动配置。PCI定义了3种地址空间:存储器空间,输入输出空间和配置空间,每个PCI设备中都有256字节的配置空间用来存放自动配置信息,当PCI插卡插入系统,BIOS将根据读到的有关该卡的信息,结合系统的实际情况为插卡分配存储地址、中断和某些定时信息。

⑥共享中断

PCI总线是采用低电平有效方式,多个中断可以共享一条中断线,而ISA总线是边沿触发方式。

⑦扩展性好

如果需要把许多设备连接到PCI总线上,而总线驱动能力不足时,可以采用多级PCI总线,这些总线上均可以并发工作,每个总线上均可挂接若干设备。因此PCI总线结构的扩展性是非常好的。由于PCI的设计是要辅助现有的扩展总线标准,因此与ISA,EISA及MCA总线完全兼容。

⑧多路复用

在PCI总线中为了优化设计采用了地址线和数据线共用一组物理线路,即多路复用。PCI接插件尺寸小,又采用了多路复用技术,减少了元件和管脚个数,提高了效率。

⑨严格规范

PCI总线对协议、时序、电气性能、机械性能等指标都有严格的规定,保证了PCI的可靠性和兼容性。由于PCI总线规范十分复杂,其接口的实现就有较高的技术难度。

- 相关百科

- 相关知识

- 相关专栏

- 停车场收费系统

- 票箱

- 现场总线控制网络技术

- 停车场收费管理系统

- 冲压弯头材料

- Std总线

- 排气管

- 隔断

- 皮带运输机

- 饮水机

- Profibus现场总线控制系统的设计与开发

- PC总线工业控制系统精粹

- 总线周期

- 工业以太网总线

- AFDX总线协议规范

- 气门导管

- 简单实用的RS-485总线光电隔离中继器设计

- 基于C8051F040和CAN总线液位控制器设计

- 基于RS485总线技术PC机与单片机多机通讯设计

- 基于RS-485总线主从分布式电阻炉温度群控系统

- 基于Wolfson音频SoCI~2C总线接口设计

- 基于LabVIEWCAN总线通信系统设计与实现

- 基于DSP和FPGA油田测井系统总线通信接口设计

- 基于RS485总线煤矿井下粉尘浓度监测系统设计

- Controlnet总线技术在水电站综合自动化中的应用

- 现场总线控制系统实际微分PID控制器的设计

- 总线电缆连接器的电压偏置及终端电阻

- VB和RS485总线的PMLSM提升监控系统设计

- 应用光纤互连以太网构建配网自动化数据通信通道方案浅析

- RS485总线技术的微机与智能仪表的双向通信设计

- CPCI总线的IEEE1394接口模块设计与应用

- CAN总线及CORBA的分布式过电压在线监测系统