数字电路及系统设计

《数字电路及系统设计》是高等教育出版社2011年6月1日出版的图书,作者是赵曙光、刘玉英、崔葛瑾。

数字电路及系统设计基本信息

| 中文名称 | 数字电路及系统设计 | 作者 | 赵曙光^刘玉英^崔葛瑾 |

|---|---|---|---|

| 出版社 | 高等教育出版社 | ISBN | 9787040322194 |

| 出版时间 | 2011年6月1日 | 定价 | 27.20元 |

| 开本 | 16 | ||

第1章 数制与码制

1.1 数制

1.1.1 计数体制

1.1.2 不同数制之间的转换

1.2 编码

1.2.1 二-十进制编码

1.2.2 可靠性编码

1.2.3 字符编码

1.3 二进制数的算术运算

1.3.1 二进制算术运算的特点

1.3.2 原码、反码、补码和补码运算

本章习题

第2章 逻辑代数基础

逻辑运算又称布尔运算布尔用数学方法研究逻辑问题,成功地建立了逻辑演算。他用等式表示判断,把推理看作等式的变换。这种变换的有效性不依赖人们对符号的解释,只依赖于符号的组合规律 。这一逻辑理论人们常称它为布尔代数。20世纪30年代,逻辑代数在电路系统上获得应用,随后,由于电子技术与计算机的发展,出现各种复杂的大系统,它们的变换规律也遵守布尔所揭示的规律。逻辑运算 (logical operators) 通常用来测试真假值。最常见到的逻辑运算就是循环的处理,用来判断是否该离开循环或继续执行循环内的指令。

2.1 基本运算、公式和定理

2.1.1 基本逻辑运算

2.1.2 公式和定理

2.2 逻辑函数的表示方法

2.2.1 真值表

2.2.2 逻辑函数表达式

2.2.3 卡诺图

2.2.4 逻辑图

2.3 逻辑函数的化简方法

2.3.1 化简的意义和最简的概念

2.3.2 公式法化简

2.3.3 图形法化简

2.3.4 具有无关项的逻辑函数化简

本章习题

第3章 逻辑门电路

3.1 概述

3.1.1 逻辑门电路的基本概念和原理

逻辑门是在集成电路(也称:集成电路)上的基本组件。

逻辑门可以用电阻、电容、二极管、三极管等分立原件构成,成为分立元件门。也可以

将门电路的所有器件及连接导线制作在同一块半导体基片上,构成集成逻辑门电路。

简单的逻辑门可由晶体管组成。这些晶体管的组合可以使代表两种信号的高低电平在通过它们之后产生高电平或者低电平的信号。

高、低电平可以分别代表逻辑上的"真"与"假"或二进制当中的1和0,从而实现逻辑运算。常见的逻辑门包括"与"门,"或"门,"非"门,"异或"门(也称:互斥或)等等。

逻辑门可以组合使用实现更为复杂的逻辑运算。

逻辑门电路是数字电路中最基本的逻辑元件。所谓门就是一种开关,它能按照一定的条件去控制信号的通过或不通过。门电路的输入和输出之间存在一定的逻辑关系(因果关系),所以门电路又称为逻辑门电路。基本逻辑关系为"与"、"或"、"非"三种。逻辑门电路按其内部有源器件的不同可以分为三大类。第一类为双极型晶体管逻辑门电路,包括TTL、ECL电路和I2L电路等几种类型;第二类为单极型MOS逻辑门电路,包括NMOS、PMOS、LDMOS、VDMOS、VVMOS、IGT等几种类型;第三类则是二者的组合BICMOS门电路。常用的是CMOS逻辑门电路

3.1.2 数字集成电路的分类和特点

3.2 半导体元件的开关特性

3.3 ttl门电路

集电极开路门,即OC门,是一种能够实现线逻辑的电路。OC与非门电路的特点是将原TTL与非门电路中的VT3管(见图1)集电极开路,并取消集成电极电阻。所以,使用OC门时,为保证电路正常工作,必须外接一只RL电阻与电源VCC相连,称为上拉电阻,如图2(a)所示。

3.3.1 ttl与非门

3.3.2 其他类型的ttl门电路

3.3.3 ttl器件的选择和使用要点

3.4 cmos门电路

3.4.1 cmos基本门电路

3.4.2 其他类型的cmos门电路

3.4.3 cmos器件的选择和使用要点

本章习题

第4章 组合逻辑电路

4.1 概述

4.2 组合逻辑电路的分析方法

4.3 常用组合逻辑电路与器件

4.3.1 编码器

编码器(encoder)是将信号(如比特流)或数据进行编制、转换为可用以通讯、传输和存储的信号形式的设备。编码器把角位移或直线位移转换成电信号,前者称为码盘,后者称为码尺。按照读出方式编码器可以分为接触式和非接触式两种;按照工作原理编码器可分为增量式和绝对式两类。增量式编码器是将位移转换成周期性的电信号,再把这个电信号转变成计数脉冲,用脉冲的个数表示位移的大小。绝对式编码器的每一个位置对应一个确定的数字码,因此它的示值只与测量的起始和终止位置有关,而与测量的中间过程无关。

4.3.2 译码器

译码器是组合逻辑电路的一个重要的器件,其可以分为:变量译码和显示译码两类。 变量译码一般是一种较少输入变为较多输出的器件,一般分为2n译码和8421BCD码译码两类。 显示译码主要解决二进制数显示成对应的十、或十六进制数的转换功能,一般其可分为驱动LED和驱动LCD两类。

4.3.3 数据选择器

4.3.4 加法器

加法器是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。在电子学中,加法器是一种数位电路,其可进行数字的加法计算。在现代的电脑中,加法器存在于算术逻辑单元(ALU)之中。 加法器可以用来表示各种数值,如:BCD、加三码,主要的加法器是以二进制作运算。由于负数可用二的补数来表示,所以加减器也就不那么必要。

加法器是为了实现加法的。

即是产生数的和的装置。加数和被加数为输入,和数与进位为输出的装置为半加器。若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。

对于1位的二进制加法,相关的有五个的量:1,被加数A,2,被加数B,3,前一位的进位CIN,4,此位二数相加的和S,5,此位二数相加产生的进位COUT。前三个量为输入量,后两个量为输出量,五个量均为1位。

对于32位的二进制加法,相关的也有五个量:1,被加数A(32位),2,被加数B(32位),3,前一位的进位CIN(1位),4,此位二数相加的和S(32位),5,此位二数相加产生的进位COUT(1位)。

要实现32位的二进制加法,一种自然的想法就是将1位的二进制加法重复32次(即逐位进位加法器)。这样做无疑是可行且易行的,但由于每一位的CIN都是由前一位的COUT提供的,所以第2位必须在第1位计算出结果后,才能开始计算;第3位必须在第2位计算出结果后,才能开始计算,等等。而最后的第32位必须在前31位全部计算出结果后,才能开始计算。这样的方法,使得实现32位的二进制加法所需的时间是实现1位的二进制加法的时间的32倍。

4.3.5 数值比较器

在数字电路中,经常需要对两个位数相同的二进制数进行比较,以判断它们的相对大小或者是否相等,用来实现这一功能的逻辑电路就成为数值比较器。

数值比较器就是对两数A、B进行比较,以判断其大小的逻辑电路。比较结果有A>B、A<B以及A=B三种情况。

1.一位数值比较器

1位数值比较器是多位比较器的基础。当A和B都是1位数时,它们只能取0或1两种值,由此可写出1位数值比较器的真值表:

由真值表得到如下逻辑表达式:

由以上逻辑表达式可画出如下图所示的逻辑电路。实际应用中,可根据具体情况选用逻辑门。

2.两位数值比较器 现在分析比较两位数字A1A0和B1B0的情况。 利用1位比较器的结果,可以列出简化的真值表如下:

为了减少符号的种类,不再使用字母L,而以(Ai>Bi)、(AiB1)=0和(A1<B1)=0作用,或门也打开,低位的比较结果直接送达输出端,即低位的比较结果决定两数谁大、谁小或者相等。

二、集成数值比较器

我们以74LS85为例来说明集成数值比较器。

1.集成数值比较器74LS85得功能 集成数值比较器74LS85是4位数值比较器,其功能如下:

从功能表可以看出,该比较器的比较原理和两位比较器的比较原理相同。两个4位数的比较是从A的最高位A3和B的最高位B3进行比较,如果它们不相等,则该位的比较结果可以作为两数的比较结果。若最高位A3=B3,则再比较次高位A2和B2,余类推。显然,如果两数相等,那么,比较步骤必须进行到最低位才能得到结果。 真值表中的输入变量包括A3与B3、A2与B2、A1与B1、A0与B0和A与B的比较结果。其中A和B是另外两个低位数,IA>B、IA<B和IA=B是它们的比较结果。设置低位数比较结果输入端是为了能与其他数值比较器连接,以便组成位数更多的数值比较器。根据1位数值比较器逻辑表达式可知:

再根据74LS85的功能表可

上式与逻辑图一致。由上式可以看出,仅对4位数进行比较时,应对IA>B、IAB=IA<B=0,IA=B=1。

2.数值比较器的位数扩展

现在来讨论一下数值比较器的位数扩展问题。数值比较器的扩展方式有串联和并联两种。

下图表示两个4位数值比较器串联而成为一个8位数值比较器。

我们知道,对于两个8位数,若高4位相同,它们的大小则由低4位的比较结果确定。因此,低4位的比较结果应作为高4位的条件,即低4位比较器的输出端应分别与高4位比较器的IA>B、IA<B、IA=B端连接。

当位数较多且要满足一定的速度要求时,可以采取并联方式。

由图可以看出,这里采用两级比较方法,将16位按高低位次序分成4组,每组4位,各组的比较是并行进行的。将每组的比较结果再经4位比较器进行比较后得出结果。显然,从数据输入到稳定输出只需两倍的4位比较器延迟时间,若用串联方式,则16位的数值比较器从输入到稳定输出需要4倍的4位比较器的延迟时间。

4.4 组合逻辑电路的设计方法

4.4.1 用ssi器件设计组合逻辑电路举例

4.4.2 用msi器件设计组合逻辑电路举例

4.5 组合逻辑电路中的竞争冒险

4.5.1 竞争冒险的产生原因和分类

4.5.2 冒险现象的判别

4.5.3 消除竞争冒险的方法

本章习题

第5章 触发器

5.1 概述

触发器(trigger)是个特殊的存储过程,它的执行不是由程序调用,也不是手工启动,而是由事件来触发,比如当对一个表进行操作( insert,delete, update)时就会激活它执行。触发器经常用于加强数据的完整性约束和业务规则等。 触发器可以从 DBA_TRIGGERS ,USER_TRIGGERS 数据字典中查到。

5.2 rs触发器的基本特性和电路结构

5.2.1 基本rs触发器

5.2.2 同步rs触发器

5.2.3 主从rs触发器

5.2.4 触发器的时间参数

5.3 d触发器

5.4 jk触发器

5.5 t触发器和t触发器

5.6 常用集成触发器及其激励功能转换

本章习题

第6章 时序逻辑电路

6.1 概述

由多个触发器和多个组合逻辑块组成的网络。常用的有:计数器、复杂的数据流动控制逻辑、运算控制逻辑、指令分析和操作控制逻辑。同步时序逻辑是设计复杂的数字逻辑系统的核心。时序逻辑借助于状态寄存器记住它目前所处的状态。在不同的状态下,即使所有的输入都相同,其输出也不一定相同。

6.1.1 时序逻辑电路的基本概念

6.1.2 时序逻辑电路的分类

6.1.3 常用的时序逻辑电路模块

6.2 时序逻辑电路的基本结构和描述方法

6.3 时序逻辑电路的一般分析方法

6.4 同步时序逻辑电路的一般设计方法

6.4.1 同步时序逻辑电路的设计

6.4.2 时序逻辑电路的asm图描述

6.4.3 状态化简的一般方法

6.4.4 状态编码分配的一般规则

6.5 常用时序逻辑器件及其应用

6.5.1 基于msi的时序电路分析和设计方法

6.5.2 集成计数器及其应用

6.5.3 集成移位寄存器及其应用

6.5.4 集成寄存器和集成锁存器

本章习题

第7章 脉冲波形的产生和整形

7.1 概述

7.2 多谐振荡器

7.2.1 cmos逻辑门组成的多谐振荡器

7.2.2 555定时器构成的多谐振荡器

7.2.3 石英晶体振荡器

石英晶体振荡器,石英谐振器简称为晶振,它是利用具有压电效应的石英晶体片制成的。这种石英晶体薄片受到外加交变电场的作用时会产生机械振动,当交变电场的频率与石英晶体的固有频率相同时,振动便变得很强烈,这就是晶体谐振特性的反应。利用这种特性,就可以用石英谐振器取代LC(线圈和电容)谐振回路、滤波器等。由于石英谐振器具有体积小、重量轻、可靠性高、频率稳定度高等优点,被应用于家用电器和通信设备中。石英谐振器因具有极高的频率稳定性,故主要用在要求频率十分稳定的振荡电路中作谐振元件。

频率范围很宽,频率稳定度在10-4~10-12范围内,经校准一年内可保持1

0-9的准确度,高质量的石英晶体振荡器,在经常校准时,频率准确可达10-11.高效能模拟与混合信号IC厂商Silicon Laboratories(芯科实验室有限公司)日前推出业界第一款支持输出频率可编程的振荡器(XO)和压控振荡器(VCXO)。Si570/1系列采用公司专利的DSPLL技术和业界标准的I2C接口,通过对I2C接口的操作,一颗器件就能产生10MHz到1.4GHz的任何输出频率,同时将均方根抖动幅度减少到0.3ps左右。Si570任意频率XO和Si571任意频率VCXO最适合需要弹性频率源的高效能应用,包括下一代网络设备、无线基站,测试与测量装置、高画质电视视频基础设施和高速数据采集装置。

硬件设计人员过去必须用多个固定频率XO、VCXO或压控SAW振荡器(VCSO),才能开发出复杂系统所需的可变频率架构,并让它们以不同频率操作。但这种方法的成本很高,需要复杂的模拟锁相回路(PLL)设计和布局,还会延长新开发产品的上市时间。

7.3 单稳态触发器

7.3.1 cmos微分型单稳态触发器

7.3.2 555定时器构成的单稳态触发器

7.3.3 可重复触发的单稳态触发器

7.3.4 集成单稳态触发器

7.3.5 单稳态触发器的应用

7.4 施密特触发器

7.4.1 用门电路组成的施密特触发器

7.4.2 常用的集成施密特触发器

7.4.3 施密特触发器的应用

本章习题

第8章 半导体存储器

8.1 概述

半导体存储器(semi-conductor memory)

是一种以半导体电路作为存储媒体的存储器,内存储器就是由称为存储器芯片的半导体集成电路组成。

按其功能可分为:随机存取存储器(简称RAM)和只读存储器(只读ROM)

RAM包括DRAM(动态随机存取存储器)和SRAM(静态随机存取存储器),当关机或断电时,其中的 信息都会随之丢失。 DRAM主要用于主存(内存的主体部分),SRAM主要用于高速缓存存储器。

ROM 主要用于BIOS存储器。

按其制造工艺可分为:双极晶体管存储器和MOS晶体管存储器。

按其存储原理可分为:静态和动态两种。

其优点是:体积小、存储速度快、存储密度高、与逻辑电路接口容易。

主要用作高速缓冲存储器、主存储器、只读存储器、堆栈存储器等。

半导体存储器的技术指标主要有:

1. 存储容量:存储单元个数M×每单元位数N

2. 存取时间:从启动读(写)操作到操作完成的时间

3. 存取周期:两次独立的存储器操作所需间隔的最小时间

4. 平均故障间隔时间MTBF(可靠性)

5. 功耗:动态功耗、静态功耗

8.1.1 分类与特点

8.1.2 主要性能指标

8.2 只读存储器

8.2.1 只读存储器的结构

8.2.2 只读存储器的编程及分类

8.3 随机存储器

8.3.1 随机存储器的基本结构

8.3.2 随机存储器的主要类型

8.3.3 静态随机存储器

一般计算机系统使用的随机存取内存(RAM)可分动态(DRAM)与静态随机存取内存(SRAM)两种,差异在于DRAM需要由存储器控制电路按一定周期对存储器刷新,才能维系数据保存,SRAM的数据则不需要刷新过程,在上电期间,数据不会丢失。

SRAM存储电路以双稳态触发器为基础,其一位存储单元类似于D锁存器。数据一经写入只要不关掉电源,则将已知保持有效。而DRAM存储电路以电容为基础,靠芯片内部电容电荷的有无来表示信息,为防止由于电容漏电所引起的信息丢失,就需要在一定的时间间隔内对电容进行充电,这种充电的过程称为DRAM的刷新。

8.3.4 动态随机存储器

8.4 存储器容量的扩展

8.5 利用存储器实现逻辑函数

本章习题

第9章 数-模转换和模-数转换

9.1 数-模转换

9.1.1 数-模转换器的基本原理

数-模转换器

digital-to-analog converter

把数字信号转换成模拟信号的转换器。简称D/A。在计算机应用中,计算机运算、加工处理的信号都是数字量,而计算机控制的对象又都是模拟量(连续变化的电压和电流),这就需要将数字信号转换成相对应的模拟信号,即使用D/A转换器。转换技术主要有R-2R梯形电阻网络方式与小数二进制权电流方式两种。D/A是计算机同外界通信的重要接口之一。

9.1.2 常用的数-模转换技术

9.1.3 数-模转换器的主要技术参数

9.1.4 集成dac的选用

9.1.5 数-模转换器输出极性的扩展

9.1.6 数-模转换器的典型应用

9.2 模-数转换

9.2.1 模-数转换器的主要参数

9.2.2 常用的模-数转换技术

9.2.3 集成adc的选用

9.2.4 采样-保持器的原理和指标

本章习题

第10章 现代数字系统的设计与实现方法

10.1 现代数字系统的主要构件--可编程逻辑器件

10.1.1 可编程器件概述

10.1.2 可编程逻辑器件的分类与特点

10.1.3 cpld的典型结构和原理

10.1.4 fpga的典型结构和原理

10.1.5 可编程逻辑器件的开发流程

10.3 现代数字系统的描述工具--硬件描述语言

10.3.1 硬件描述语言verilog-hdl简介

10.3.2 硬件描述语言vhdl简介

10.4 现代数字系统的设计方法和流程

10.4.1 传统的电路设计流程及其困境

10.4.2 现代电子设计的基本流程和方法

本章习题

参考文献

数字电路及系统设计造价信息

数字电路及系统设计常见问题

-

分频就是用同一个时钟信号通过一定的电路结构转变成不同频率的时钟信号。二分频就是通过有分频作用的电路结构,在时钟每触发2个周期时,电路输出1个周期信号。比如用一个脉冲时钟触发一个计数器,计数器每计2个数...

-

Multisim http://www.verycd.com/topics/2754295/下载地址NI Multisim 10用软件的方法虚拟电子与电工元器件,虚拟电子与电工仪器和仪表,实现了“软件...

-

你好:数字电路有很多种。你想说的可能是数字开关电路,利用它可以制成晶体管无触点开关(或称电子开关)。它是利用三极管的截止与饱和状态实现“关”和“开”。三极管饱和导通时ce之间阻抗近似为0(ce短路),...

数字电路及系统设计文献

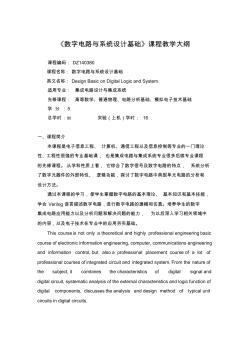

《数字电路与系统设计基础》课程教学大纲

《数字电路与系统设计基础》课程教学大纲

《数字电路与系统设计基础》课程教学大纲 课程编码: DZ140380 课程名称: 数字电路与系统设计基础 英文名称: Design Basic on Digital Logic and System 适用专业: 集成电路设计与集成系统 先修课程: 高等数学、普通物理、电路分析基础、模拟电子技术基础 学 分 :5 总学时:80 实验(上机)学时: 16 一、课程简介 本课程是电子信息工程、 计算机、通信工程以及信息控制等专业的一门理论 性、工程性很强的专业基础课, 也是集成电路与集成系统专业很多后续专业课程 的先修课程。从学科性质上看, 它综合了数字信号及数字电路的特点, 系统分析 了数字元器件的外部特性、 逻辑功能,探讨了数字电路中典型单元电路的分析和 设计方法。 通过本课程的学习,使学生掌握数字电路的基本理论、 基本知识和基本技能, 学会 Verilog语言描述数字电路,进行数字电路

数字电路系统设计中的抗干扰技术

数字电路系统设计中的抗干扰技术

本文首先介绍了干扰在数字电路系统中的危害,其次分析了形成干扰的原因,最后提出了相应的抗干扰技术,并且分别给出了硬件抗干扰技术和软件抗干扰技术的设计方案。

- 相关百科

- 相关知识

- 相关专栏

- L17轴承

- NTN NUP409轴承

- 分子扩散焊

- 7220B/DF轴承

- NU228ECJ轴承

- 贝尔图像插值和压缩算法原理及应用

- NTN 2305轴承

- SKF 3318轴承

- 水工设计手册--第七卷水电站建筑物

- SKF 3320轴承

- SKF NU324EC轴承

- NTN 51244轴承

- NTN UCF205轴承

- NTN N2244轴承

- NSK 7004ADT轴承

- NSK23288CAKE4轴承

- 张潘明污水处理厂初步设计说明书(水质工程学课程)

- 云南洱海桃溪河口净化工程的设计思路及初步净化效果

- 增设钢牛腿在连续独柱墩桥梁抗倾覆加固设计中的应用

- 智能建筑火灾自动报警与消防联动系统设计及应用效果

- 余杭某供电营业所生产营业用房工程建筑设计招标文件

- 中国建筑抗震设计规范的演变与展望

- 中国恩菲工程技术有限公司中国有色工程设计总院

- 有线电视广播系统运行维护规程编制情况和宣贯要点

- 在项目成本控制中的实践与探索工程项目成本管理系统

- 园林景观及配套设施标工程施工组织设计建筑施工

- 再谈VRV空调系统设计与施工中有关问题的解决方法

- 有关CAD技术在水利工程设计中的实际应用方法

- 中国电工技术学会电力系统控制与保护专业委员会成立

- 用于制冷系统稳定运行时制冷剂分布测试的新方法

- 中、小跨径钢筋混凝土拱桥现浇支架(拱架)设计指南

- 中国国家博物馆改扩建设计回顾及学术研讨会