热设计功耗

热设计功耗基本信息

| 中文名 | 热设计功耗 | 外文名 | Thermal Design Power |

|---|---|---|---|

| 别 名 | 散热设计功耗 | 简 称 | TDP |

| 适用行业 | 计算机系统厂商,散热片/风扇厂商等 | 释 义 | CPU电流热效应以及CPU工作时产生的单位时间热量 |

TDP是CPU电流热效应以及CPU工作时产生的单位时间热量。TDP功耗通常作为电脑(台式)主板设计、笔记本电脑散热系统设计、大型电脑散热设计等散热/降耗设计的重要参考指标。TDP越大,表明CPU在工作时会产生的单位时间热量越大。对于散热系统来说,需要将TDP作为散热能力设计的最低标准,也就是散热系统至少要能散出TDP数值所表示的单位时间热量。例如,一个笔记型电脑的CPU散热系统可能被设计为20W TDP,这代表了它可以消散20W的热功率(可能是通过主动式散热手段如使用风扇,或是被动式散热手段如热管散热)而不超出芯片的最大结温。

TDP一旦确定,就确保了电脑在不超出热维护的情况下有能力运行程序,而不需要安装一个“强悍”,同时多花费添置没有什么额外效果的散热系统。

热设计功耗造价信息

可配置TDP(cTDP)也称为可编程TDP或TDP功耗上限,是后续英特尔移动处理器(截至2014年1月)和AMD处理器(截至2012年6月)的运行模式,允许调整其TDP值。通过修改处理器行为及其性能级别,可以改变处理器的功耗,同时改变其TDP。这样,处理器可以在更高或更低的性能水平下运行,具体取决于可用的制冷能力和所需的功耗。

支持cTDP的英特尔处理器提供三种操作模式:

-

标称TDP- 这是处理器的额定频率和TDP。

-

cTDP down- 当需要更冷或更安静的操作模式时,此模式指定较低的TDP和较低的保证频率与标称模式。

-

cTDP启动- 当额外冷却可用时,此模式指定较高的TDP和较高的保证频率(相对于标称模式)。

例如,某些移动Haswell处理器支持cTDP up,cTDP down或两种模式。作为另一个例子,一些AMDOpteron处理器和KaveriAPU可以配置为较低的TDP值。IBM的POWER8处理器通过其嵌入式片上控制器(OCC)实现了类似的功率封顶功能。 2100433B

热设计功耗的含义是当芯片达到最大负荷的时候〔单位为瓦(W)〕热量释放的指标,是电脑的冷却系统必须有能力驱散热量的最大限度,但不是芯片释放热量的功率。

一般TDP主要应用于CPU,CPUTDP值对应系列CPU 的最终版本在满负荷(CPU 利用率为100%的理论上)可能会达到的最高散热热量,散热器必须保证在处理器TDP最大的时候,处理器的温度仍然在设计范围之内。

注意:由于CPU的核心电压与核心电流时刻都处于变化之中,这样CPU的实际功耗(其值:功率P=电流I×电压U)也会不断变化,因此TDP值并不等同于CPU的实际功耗,更没有算术关系。

举例来说,Pentium E2160 TDP为65W,而实际运行中的平均功耗仅19W。

由于厂商提供的TDP数值肯定留有一定的余地,对于具体的处理器而言,TDP应该大于CPU的峰值功耗。

热设计功耗常见问题

-

普通电热毯用一夜耗0.32度电到0.48度电。 一般普通电热毯是40-60W之间,也就是40W的电热毯一个小时用电在0.04度电,60W电热毯一个小时用电在0.06度电,一个晚上算8个小时,40W时:...

-

工作功率P=UI,取决于设备电压和电阻,电热膜的电阻值可以用欧姆表从温控器端的接头端测量得到,一般实际电阻与平方功率和面积乘积的结果会有出入,所以,在电热膜实际铺装完毕后,施工人员会给出实际铺装功率。...

-

输入功率1800W,制冷功率4000W不错,这里的制冷功率指的是制冷输出功率,也就是制冷量,制暖输出功率与制冷差不多。耗电是根据输入功率计算,内机上有铭牌标注制暖输入功率或者制暖消耗功率的,计算公式为...

大多数计算机设备容量用伏安(VA)表示,最近有些计算机开始用瓦特(W)表示容量(最著名的DEC和IBM)。但总体而言还是用VA的多。所以不断电系统(UPS)用VA表示容量更能反映出其和负载的匹配程度。而TDP是指CPU电流热效应以及其他形式产生的热能,他们均以热的形式释放。CPU的功耗很大程度上是对主板提出的要求,要求主板能够提供相应的电压和电流;而TDP是对散热系统提出要求,要求散热系统能够把CPU发出的热量散掉,也就是说,TDP是要求CPU的散热系统必须能够驱散的最小总热量。

热设计功耗文献

超低功耗超声波热量表的设计

超低功耗超声波热量表的设计

低功耗与高精度是热量表的关键。本文设计了基于超低功耗单片机MSP430系列为主要控制器和高精度TDC-GP21为主测量芯片的的小管道超声波式热量表。液晶汉显,用户界面良好。通信方式多样,抄表方便。实验表明,本设计具有超功耗低、精度高、对外界环境要求低,易于集中管理等优点。

低功耗超声波热量表的设计与实现

低功耗超声波热量表的设计与实现

该文设计了一种低功耗高精度的超声波热量表。热量表采用MSP430作为MCU,使用时间测量芯片TDC-GP21来测量超声波前向和后向传播时间,利用热敏电阻PT1000测量进水口和出水口处温度。文中从硬件设计入手,探讨了热量表的组成原理,并基于该硬件设计了热量计算软件。实际测试结果表明,该热量表具有较高的计量精度和良好的稳定性。

低功耗IC设计

微处理器的低功耗设计技术,首先必须了解它的功耗来源。其中时钟单元(Clock)功耗最高,因为时钟单元有时钟发生器、时钟驱动、时钟树和钟控单元的时钟负载;数据通路(Datapath)是仅次于时钟单元的部分,其功耗主要来自运算单元、总线和寄存器堆。除了上述两部分,还有存储单元(Memory),控制部分和输入/输出(Control,I/O)。存储单元的功耗与容量相关。

CMOS电路功耗主要由3部分组成:电路电容充放电引起的动态功耗,结反偏时漏电流引起的功耗和短路电流引起的功耗。其中,动态功耗是最主要的,占了总功耗的90%以上。

常用的低功耗设计技术

低功耗设计足一个复杂的综合性课题。就流程而言,包括功耗建模、评估以及优化等;就设计抽象层次而言,包括自系统级至版图级的所有抽象层次。同时,功耗优化与系统速度和面积等指标的优化密切相关,需要折中考虑。下面讨论常用的低功耗设计技术。

1) 动态电压调节

动态功耗与工作电压的平方成正比,功耗将随着工作电压的降低以二次方的速度降低,因此降低工作电压是降低功耗的有力措施。但是,仅仅降低工作电压会导致传播延迟加大,执行时间变长。然而,系统负载是随时间变化的,因此并不需要微处理器所有时刻都保持高性能。动态电压调节DVS(Dynarnic Voltage Scaling)技术降低功耗的主要思路是根据芯片工作状态改变功耗管理模式,从而在保证性能的基础上降低功耗。在不同模式下,工作电压可以进行调整。为了精确地控制DVS,需要采用电压调度模块来实时改变工作电压,电压调度模块通过分析当前和过去状态下系统工作情况的不同来预测电路的工作负荷。

2) 门控时钟和可变频率时钟

在微处理器中,很大一部分功耗来自时钟。时钟是惟一在所有时间都充放电的信号,而且很多情况下引起不必要的门的翻转,因此降低时钟的开关活动性将对降低整个系统的功耗产牛很大的影响。门控时钟包括门控逻辑模块时钟和门控寄存器时钟。门控逻辑模块时钟对时钟网络进行划分,如果在当前的时钟周期内,系统没有用到某些逻辑模块,则暂时切断这些模块的时钟信号,从而明显地降低开关功耗。采用"与"门实现的时钟控制电路。门控寄存器时钟的原理是当寄存器保持数据时,关闭寄存器时钟,以降低功耗。然而,门控时钟易引起毛刺,必须对信号的时序加以严格限制,并对其进行仔细的时序验证。

另一种常用的时钟技术就是可变频率时钟。它根据系统性能要求,配置适当的时钟频率以避免不必要的功耗。门控时钟实际上是可变频率时钟的一种极限情况(即只有零和最高频率两种值),因此,可变频率时钟比门控时钟技术更加有效,但需要系统内嵌时钟产生模块PLL,增加了设计复杂度。去年Intel公司推出的采用先进动态功耗控制技术的Montecito处理器,就利用了变频时钟系统。该芯片内嵌一个高精度数字电流表,利用封装上的微小电压降计算总电流;通过内嵌的一个32位微处理器来调整主频,达到64级动态功耗调整的目的,大大降低了功耗。

3) 并行结构与流水线技术

并行结构的原理是通过牺牲面积来降低功耗。将一个功能模块复制为n(n≥2)个相同的模块,这些模块并行计算后通过数据选择器选择输出,采用二分频的并行结构。

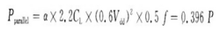

并行设计后,由于有多个模块同时工作,提高了吞吐能力,可以把每个模块的速度降低为原来的l/n。根据延时和工作电压的线性关系,工作电压可以相应降低为原来的l/n,电容增大为原来的n倍,工作频率降低为原来的l/n,根据式(1)功耗降低为原来的1/n2。并行设计的关键是算法设计,一般算法中并行计算的并行度往往比较低,并行度高的算法比较难开发。例如:若原模块的功耗为P=a×CL×V2dd×f,采用二分频结构,由于增加了一个模块和数据选择器,整个电容负载为2.2CL,工作频率为f/2,工作电压可以降为O.6 V,则其功耗为:

由此可见,二分频并行结构在保持原有电路性能的同时降低了60%的功耗。

流水线技术本质上也是一种并行。把某一功能模块分成n个阶段进行流水作业,每个阶段由一个子模块来完成,在子模块之间插入寄存器,如图5所示。若工作频率不变,对某个模块的速度要求仅为原来的1/n,则工作电压可以降低为原来的1/n,电容的变化不大(寄存器面积占的比例很小),功耗可降低为原来的1/n2,面积基本不变,但增加了控制的复杂度。例如,若原模块的功耗为P=α×C1×V2dd×f,采用流水线技术,由于增加了寄存器,整个电容负载为1.2CL,工作频率不变,工作电压降为0.6 V,则其功耗为

:

由此可见,流水线技术能显著降低系统功耗。

通过流水线技术和并行结构降低功耗的前提是电路工作电压可变。如果工作电压固定,则这两种方法只能提高电路的工作速度,并相应地增加了电路的功耗。在深亚微米工艺下,工作电压已经比较接近阈值电压,为了使工作电压有足够的下降空间,应该降低阔值电压;但是随着阈值电压的降低,亚阈值电流将呈指数增长,静态功耗迅速增加。因此,电压的下降空间有限。

4) 低功耗单元库

设计低功耗单元库是降低功耗的一个重要方法,包括调整单元尺寸、改进电路结构和版图设计。用户可以根据负载电容和电路延时的需要选择不同尺寸的电路来实现,这样会导致不同的功耗,因此可以根据需要设计不同尺寸的单元。同时,为常用的单元选择低功耗的实现结构,如触发器、锁存器和数据选择器等。

5) 低功耗状态机编码

状态机编码对信号的活动性具有重要影响,通过合理选择状态机状态的编码方法,减少状态切换时电路的翻转,可以降低状态机的功耗。其原则是:对于频繁切换的相邻状态,尽量采用相邻编码。例如:Gray码在任何两个连续的编码之间只有一位的数值不同,在设计计数器时,使用Gray码取代二进制码,则计数器的改变次数几乎减少一半,显著降低了功耗;在访问相邻的地址空间时,其跳变次数显著减少,有效地降低了总线功耗。

6) Cache的低功耗设计

作为现代微处理器中的重要部件,Cache的功耗约占整个芯片功耗的30%~60%,因此设计高性能、低功耗的Cach结构,对降低微处理器的功耗有明显作用。Cache低功耗设计的关键在于降低失效率,减少不必要的操作。通常用来降低Cache功耗的方法有以下两种:一种是从存储器的结构出发,设计低功耗的存储器,例如采用基于CAM的Cache结构;另一种是通过减少对Cache的访问次数来降低功耗。

以上主要是从硬件的角度来实现功耗的降低。除了硬件方法,通过软件方面的优化,也能显著地降低功耗。例如:在Crusoe处理器中,采用高效的超长指令(VLIW)、代码融合(Code Morphing)技术、LongRun电源管理技术和RunCooler工作温度自动调节等创新技术,获得了良好的低功耗效果。

在嵌入式系统的设计中,低功耗设计(Low-Power Design)是许多设计人员必须面对的问题。

1)选用节能的微处理器 同样的工作状态,电源电压不同,功耗是非线性增加的。

我们是在CPU的性能(Performance)和功耗(Power Consumption)方面进行比较和选择。通常可以采用每执行1M次指令所消耗的能量来进行衡量,即Watt/MIPS。但是,这仅仅是一个参考指标,实际上各个CPU的体系结构相差很大,衡量性能的方式也不尽相同,所以,我们还应该进一步分析一些细节。 我们把CPU的功率消耗分为两大部分:内核消耗功率PCORE和外部接口控制器消耗功率PI/O,总的功率等于两者之和,即P=PCORE+PI /O。对于PCORE,关键在于其供电电压和时钟频率的高低;对于PI/O来讲,除了留意各个专门I/O控制器的功耗外,还必须关注地址和数据总线宽度。

2)尽量选用CMOS集成电路 CMOS集成电路(Complementary Metal Oxide Semiconductor)即互补金属-氧化物-半导体集成电路,它最大的优点是微功耗(静态功耗几乎为零),其次的优点是输出逻辑电平摆幅大,因而抗干扰能力强,同时它的工作温度范围也宽,因此CMOS电路一开始出现就和低功耗便携式仪器仪表结下了不解之缘。

3)、采用电池低电压供电 系统功耗和系统的供电电压存在着一定的函数关系。供电电压越高,系统功耗也就越大。目前已经出现了不少低电压供电(小于4.5V)的单片机及其外围电路,工作电压可低至1.8V。在1.8V~6V之间均可正常工作,而且对于测量精度没有影响。 在设计开发中要注意,单片机电源电压可以从6V降到1.8V,工作期间电压可以在该范围波动,但是国内的仿真器还达不到这个要求,一般都在5V下仿真工作。这时候的仿真和真正的工作状态是有区别的,所以单片机系统设计完之后一定要进行低电压测试,避免仿真时可以用,实际应用时出现问题。

4)、尽量使用"高速低频"工作方式 低功耗单片微机系统中几乎全部采用的是CMOS器件,而CMOS集成电路由自己的结构所决定,它静态功耗几乎为零,仅在逻辑状态发生转换期间,电路有电流流过。所以它的动态功耗和它的逻辑转换频率成正比,和电路的逻辑状态转换时间成正比。所以,CMOS集成电路从降低功耗的角度上来说应当快速转换,低频率地工作。

5)、充分利用微控制器上集成的功能 微控制器已经将许多硬件集成到一块芯片之中,使用这些功能比用扩展方式扩展外围电路要有效得多。首先单片化的成本要比使用扩展方式低,而且性能更好。如外围器件的驱动电压很难降低到微控制器芯片的水平,微控制器可以降低到1.8V,外围电路降到3V恐怕有相当多的芯片就会工作不稳定,而微控制器内部集成的硬件却可以有更好的电压适应能力。

6)、选用低功耗高效率的外围器件和电路 在必须选择使用某些外围器件时,尽可能选择低功耗、低电压、高效率的外围器件,象LCD液晶显示器、EEPROM等,这样是为了降低系统的总体功耗。此外还尽量选用低功耗及高效率的电路形式。低功耗的电路以低功耗为主要技术指标,它不盲目追求高速度和大的驱动能力,以满足要求为限度,因而电路的工作电流都比较小。

低功耗设计足一个复杂的综合性课题,就流程而言,包括功耗建模、评估以及优化等;就设计抽象层次而言,包括自系统级至版图级的所有抽象层次。同时,功耗优化与系统速度和面积等指标的优化密切相关,需要折中考虑。

动态电压调节

动态功耗与工作电压的平方成正比,功耗可随着工作电压的降低以二次方的速度降低,因此降低工作电压是降低功耗的有力措施。但是,仅仅降低工作电压会导致传播延迟加大,执行时间变长。然而,系统负载是随时间变化的,因此并不需要微处理器所有时刻都保持高性能。动态电压调节DVS(Dynarnic Voltage Scaling)技术降低功耗的主要思路是根据芯片工作状态改变功耗管理模式,从而在保证性能的基础上降低功耗。在不同模式下,工作电压可以进行调整。为了精确地控制DVS,需要采用电压调度模块来实时改变工作电压,电压调度模块通过分析当前和过去状态下系统工作情况的不同来预测电路的工作负荷。

两种时钟

在微处理器中,很大一部分功耗来自时钟。时钟是惟一在所有时间都充放电的信号,而且很多情况下引起不必要的门的翻转,因此降低时钟的开关活动性可以对降低整个系统的功耗产生很大的影响。门控时钟包括门控逻辑模块时钟和门控寄存器时钟。门控逻辑模块时钟对时钟网络进行划分,如果在当前的时钟周期内,系统没有用到某些逻辑模块,则暂时切断这些模块的时钟信号,从而明显地降低开关功耗。门控寄存器时钟的原理是当寄存器保持数据时,关闭寄存器时钟,以降低功耗。然而,门控时钟易引起毛刺,必须对信号的时序加以严格限制,并对其进行仔细的时序验证。

另一种常用的时钟技术就是可变频率时钟。它根据系统性能要求,配置适当的时钟频率以避免不必要的功耗。门控时钟实际上是可变频率时钟的一种极限情况(即只有零和最高频率两种值),因此,可变频率时钟比门控时钟技术更加有效,但需要系统内嵌时钟产生模块PLL,增加了设计复杂度。Intel公司推出的采用先进动态功耗控制技术的Montecito处理器,就利用了变频时钟系统。该芯片内嵌一个高精度数字电流表,利用封装上的微小电压降计算总电流;通过内嵌的一个32位微处理器来调整主频,达到64级动态功耗调整的目的,大大降低了功耗。

两种技术

并行结构的原理是通过牺牲面积来降低功耗。将一个功能模块复制为n(n≥2)个相同的模块,这些模块并行计算后通过数据选择器选择输出,采用二分频的并行结构。

并行设计后,由于有多个模块同时工作,提高了吞吐能力,可以把每个模块的速度降低为原来的l/n。根据延时和工作电压的线性关系,工作电压可以相应降低为原来的l/n,电容增大为原来的n倍,工作频率降低为原来的l/n,根据式(1)功耗降低为原来的1/n2。并行设计的关键是算法设计,一般算法中并行计算的并行度往往比较低,并行度高的算法比较难开发。例如:若原模块的功耗为P=a×CL×V2dd×f,采用二分频结构,由于增加了一个模块和数据选择器,整个电容负载为2.2CL,工作频率为f/2,工作电压可以降为O.6 V。由此可见,二分频并行结构在保持原有电路性能的同时降低了60%的功耗。

流水线技术本质上也是一种并行。把某一功能模块分成n个阶段进行流水作业,每个阶段由一个子模块来完成,在子模块之间插入寄存器。若工作频率不变,对某个模块的速度要求仅为原来的1/n,则工作电压可以降低为原来的1/n,电容的变化不大(寄存器面积占的比例很小),功耗可降低为原来的1/n2,面积基本不变,但增加了控制的复杂度。例如,若原模块的功耗为P=α×C1×V2dd×f,采用流水线技术,由于增加了寄存器,整个电容负载为1.2CL,工作频率不变,工作电压降为0.6 V。由此可见,流水线技术能显著降低系统功耗。

通过流水线技术和并行结构降低功耗的前提是电路工作电压可变。如果工作电压固定,则这两种方法只能提高电路的工作速度,并相应地增加了电路的功耗。在深亚微米工艺下,工作电压已经比较接近阈值电压,为了使工作电压有足够的下降空间,应该降低阔值电压;但是随着阈值电压的降低,亚阈值电流可能呈指数增长,静态功耗迅速增加。因此,电压的下降空间有限。

低功耗单元库

设计低功耗单元库是降低功耗的一个重要方法,包括调整单元尺寸、改进电路结构和版图设计。用户可以根据负载电容和电路延时的需要选择不同尺寸的电路来实现,这样会导致不同的功耗,因此可以根据需要设计不同尺寸的单元。同时,为常用的单元选择低功耗的实现结构,如触发器、锁存器和数据选择器等。

状态机编码

状态机编码对信号的活动性具有重要影响,通过合理选择状态机状态的编码方法,减少状态切换时电路的翻转,可以降低状态机的功耗。其原则是:对于频繁切换的相邻状态,尽量采用相邻编码。例如:Gray码在任何两个连续的编码之间只有一位的数值不同,在设计计数器时,使用Gray码取代二进制码,则计数器的改变次数几乎减少一半,显著降低了功耗;在访问相邻的地址空间时,其跳变次数显著减少,有效地降低了总线功耗。

低功耗设计

作为现代微处理器中的重要部件,Cache的功耗约占整个芯片功耗的30%~60%,因此设计高性能、低功耗的Cach结构,对降低微处理器的功耗有明显作用。Cache低功耗设计的关键在于降低失效率,减少不必要的操作。通常用来降低Cache功耗的方法有以下两种:一种是从存储器的结构出发,设计低功耗的存储器,例如采用基于CAM的Cache结构;另一种是通过减少对Cache的访问次数来降低功耗。

以上主要是从硬件的角度来实现功耗的降低。除了硬件方法,通过软件方面的优化,也能显著地降低功耗。例如:在Crusoe处理器中,采用高效的超长指令(VLIW)、代码融合(Code Morphing)技术、LongRun电源管理技术和RunCooler工作温度自动调节等创新技术,获得了良好的低功耗效果。

- 相关百科

- 相关知识

- 相关专栏

- 热负荷图

- 热负荷持续曲线

- 热质交换原理与设备(第三版)

- 热质交换原理与设备(第二版)

- 热质交换原理与设备

- 热质量

- 热轧 H 型钢桩

- 热轧型钢表面质量一般要求

- 热轧测厚仪

- 热轧辊

- 热轧钢

- 热轧钢板带轧辊

- 热轧钢板表面质量的一般要求

- 热轧钢棒尺寸

- 热轧钢管生产知识问答

- 热边界层

- 分形DGS单元结构设计及其在微带电路中的应用

- 逆变TIG焊机接触引弧电路的设计(引弧电路)

- 可替代现有隔热保温材料的新型材料

- 中国机械工程学会授予材料热处理工程师资格人员名单

- 以MSP430FW427为核心的远程数字水表设计

- 新型基于热力学法的水泵效率数学模型及应用

- 引江济淮工程淠河总干渠以北安徽段截污导流工程设计

- 中华大厦五层宏远公司办公室内装修工程施工组织设计

- 原来这就是辨别冷热水管正确方法商家终于肯说实话了

- 招远电视台制作播出系统数字化改造工程的设计与实践

- 全热回收地源热泵空调机组的系统及工程方案设计

- 展览馆装饰工程消防改造施工组织设计方案(91页)

- 支持群体设计的工程数据库管理系统的结构及实现

- 智能建筑工程设计中的机电设备集成配置系统总体设计

- 中国石化北京设计院标准工艺装置管道垫片选用规定

- 中航格澜阳光花园一期门禁对讲建设项目施工组织设计