IC设计工程师职业要求

教育培训:

微电子、电子相关专业本科以上。

工作经验:

具有一定的模拟电路基础,有数模混合电路设计经验;良好的电子电路分析能力;具有soc的设计和验证的经验;精通Verilog,Tcl,C,Perl等设计语言;具有团队协作和良好的沟通能力。在IC设计行业, 人才同样是分层次的, 目前国内的大部分设计人员还属于一个很基础的层次, 主要工作是在前端设计的基础上, 而那些能够设计整个IC内部总体结构的前端设计师则非常少。后者才是更容易获得高薪的人才, 但这些人才不仅需要扎实的基础知识, 更需要很多宝贵的工作经验来培养。

IC设计工程师造价信息

负责数字电路的规格定义、RTL代码编写、验证、综合、时序分析、可测性设计;

负责进行电路设计、仿真以及总体布局和修改;

制作IC芯片功能说明书;

负责与版图工程师协作完成版图设计;

提供技术支持。

集成电路是信息产业的核心技术之一,是实现把我国信息产业做大做强的战略目标的关键。近期发布的“国家中长期科学和技术发展规划纲要”和“国民经济和社会发展第十一个五年规划纲要”,都把大力发展IC技术和产业放在突出重要的位置。因此IC设计工程师的前途光明。

IC设计工程师职业要求常见问题

-

(1)工程师发表论文,得看你评的是什么级别的工程,中级工程师,高级工程师,助理工程师?(2)一般来说,就是高级工程师的话,发表两篇国家级期刊,或者一篇省级期刊,一篇国家级期刊,刊物正规的话,不是垃圾期...

-

语言要求: 英语 熟练 职位描述:1、勘探井地质日报整理,区域地质资料整理、分析;2、现场地质相关工作支持(现场勘探、井下调研、现场地质监督); 3、煤层气勘探开发项目前期地质评价研究及工程部署。主要...

-

没有取消。根据人力资源部颁布的国家职业资格名录,有造价工程师。详见如下文件

IC设计处于集成电路产业的龙头地位,对产业整体的发展起着带动作用。 到2010年中国半导体市场将占世界总需求量的6%,位居全球第四。未来几年内中国芯片生产有望每年以魂2%的速度递增,这大大高于全球10%的平均增长速度。目前,中国现有400多所高校设置了计算机系, 新近又特批了51所商业化运作的软件学院。但这些软件学院和计算机系培养的是程序员。中国目前只有十来所大学能够培养IC设计专业的学生。因此IC设计专业人才处于极度供不应求的状态。可以这样说,这正是我国很大程度上没有足够的IC卡设计人才的根源。

IC设计工程师职业要求文献

土木工程师职业要求

土木工程师职业要求

土木工程师职业要求 学历 需要拥有土木工程、 交通工程、 暖通工程、 给水排水工程等专业, 本科或本科以上学历; [1] 能力 一般要求五到十年不等土建施工、房产开发等施工现场管理、技术质量现场监管经验, 熟悉土木工程行业专业知识、 技术规范, 施工工艺及工程造价的预决算方法, 并能独立完成 实践操作; 具有较强的图纸审核能力和计算机操作技能, 能熟练运用 CAD制图等软件; 具备 良好的组织管理能力、 临场应变能力、 分析规划能力、 统筹协调能力、 沟通表达能力等; [1] 职称与证书 在职业资格认证上往往需要具有初级或中级以上技术职称,并根据具体工作性质的不 同,要求从业者持有注册建筑师、注册土木工程师、注册结构工程师等相关注册证书; [1] 其他方面 由于经常参与现场勘查、 管理实践等, 有较大的工作强度和一定的工作压力, 需要兼顾 协调多方关系, 故还需从业者具有积极向上的精神状态

软件工程师职业道德和职业操守0120

软件工程师职业道德和职业操守0120

软件工程师职业道德和职业操守 做一个合格的 IT 从业者 一、 软件工程师的基本素质 所谓素质是指事物本身所具备的性质和特征。 对于软件工程师而言, 下面十 点是最基本的素质要求: 1. 有高度的责任心和强烈的使命感。 2. 有自觉的规范化和标准化意识。 3. 有强烈的相互协作的团队精神。 4. 有良好的和同事沟通的能力。 5. 正确对待客户需求,认真弄懂客户需求,不任意解释客户需求。 6. 有自觉的保密意识和产权意识。 7. 通过实践养成良好的文档习惯。 8. 通过学习和总结而提升创新精神和创新能力。 9. 服从上级主管工作安排。 10. 具有软件工程的概念。 二、 软件工程师的基本修养 所谓修养,一般是指自我锻炼和自我培养, 目的是达到更高的水准, 以期符 合社会的需求。 修养的高低, 也体现了一个人的水平和格调。 下面十项要求是软 件工程师不断追求的目标,也是判断软件工程师是否成熟的

低功耗IC设计

微处理器的低功耗设计技术,首先必须了解它的功耗来源。其中时钟单元(Clock)功耗最高,因为时钟单元有时钟发生器、时钟驱动、时钟树和钟控单元的时钟负载;数据通路(Datapath)是仅次于时钟单元的部分,其功耗主要来自运算单元、总线和寄存器堆。除了上述两部分,还有存储单元(Memory),控制部分和输入/输出(Control,I/O)。存储单元的功耗与容量相关。

CMOS电路功耗主要由3部分组成:电路电容充放电引起的动态功耗,结反偏时漏电流引起的功耗和短路电流引起的功耗。其中,动态功耗是最主要的,占了总功耗的90%以上。

常用的低功耗设计技术

低功耗设计足一个复杂的综合性课题。就流程而言,包括功耗建模、评估以及优化等;就设计抽象层次而言,包括自系统级至版图级的所有抽象层次。同时,功耗优化与系统速度和面积等指标的优化密切相关,需要折中考虑。下面讨论常用的低功耗设计技术。

1) 动态电压调节

动态功耗与工作电压的平方成正比,功耗将随着工作电压的降低以二次方的速度降低,因此降低工作电压是降低功耗的有力措施。但是,仅仅降低工作电压会导致传播延迟加大,执行时间变长。然而,系统负载是随时间变化的,因此并不需要微处理器所有时刻都保持高性能。动态电压调节DVS(Dynarnic Voltage Scaling)技术降低功耗的主要思路是根据芯片工作状态改变功耗管理模式,从而在保证性能的基础上降低功耗。在不同模式下,工作电压可以进行调整。为了精确地控制DVS,需要采用电压调度模块来实时改变工作电压,电压调度模块通过分析当前和过去状态下系统工作情况的不同来预测电路的工作负荷。

2) 门控时钟和可变频率时钟

在微处理器中,很大一部分功耗来自时钟。时钟是惟一在所有时间都充放电的信号,而且很多情况下引起不必要的门的翻转,因此降低时钟的开关活动性将对降低整个系统的功耗产牛很大的影响。门控时钟包括门控逻辑模块时钟和门控寄存器时钟。门控逻辑模块时钟对时钟网络进行划分,如果在当前的时钟周期内,系统没有用到某些逻辑模块,则暂时切断这些模块的时钟信号,从而明显地降低开关功耗。采用"与"门实现的时钟控制电路。门控寄存器时钟的原理是当寄存器保持数据时,关闭寄存器时钟,以降低功耗。然而,门控时钟易引起毛刺,必须对信号的时序加以严格限制,并对其进行仔细的时序验证。

另一种常用的时钟技术就是可变频率时钟。它根据系统性能要求,配置适当的时钟频率以避免不必要的功耗。门控时钟实际上是可变频率时钟的一种极限情况(即只有零和最高频率两种值),因此,可变频率时钟比门控时钟技术更加有效,但需要系统内嵌时钟产生模块PLL,增加了设计复杂度。去年Intel公司推出的采用先进动态功耗控制技术的Montecito处理器,就利用了变频时钟系统。该芯片内嵌一个高精度数字电流表,利用封装上的微小电压降计算总电流;通过内嵌的一个32位微处理器来调整主频,达到64级动态功耗调整的目的,大大降低了功耗。

3) 并行结构与流水线技术

并行结构的原理是通过牺牲面积来降低功耗。将一个功能模块复制为n(n≥2)个相同的模块,这些模块并行计算后通过数据选择器选择输出,采用二分频的并行结构。

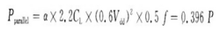

并行设计后,由于有多个模块同时工作,提高了吞吐能力,可以把每个模块的速度降低为原来的l/n。根据延时和工作电压的线性关系,工作电压可以相应降低为原来的l/n,电容增大为原来的n倍,工作频率降低为原来的l/n,根据式(1)功耗降低为原来的1/n2。并行设计的关键是算法设计,一般算法中并行计算的并行度往往比较低,并行度高的算法比较难开发。例如:若原模块的功耗为P=a×CL×V2dd×f,采用二分频结构,由于增加了一个模块和数据选择器,整个电容负载为2.2CL,工作频率为f/2,工作电压可以降为O.6 V,则其功耗为:

由此可见,二分频并行结构在保持原有电路性能的同时降低了60%的功耗。

流水线技术本质上也是一种并行。把某一功能模块分成n个阶段进行流水作业,每个阶段由一个子模块来完成,在子模块之间插入寄存器,如图5所示。若工作频率不变,对某个模块的速度要求仅为原来的1/n,则工作电压可以降低为原来的1/n,电容的变化不大(寄存器面积占的比例很小),功耗可降低为原来的1/n2,面积基本不变,但增加了控制的复杂度。例如,若原模块的功耗为P=α×C1×V2dd×f,采用流水线技术,由于增加了寄存器,整个电容负载为1.2CL,工作频率不变,工作电压降为0.6 V,则其功耗为

:

由此可见,流水线技术能显著降低系统功耗。

通过流水线技术和并行结构降低功耗的前提是电路工作电压可变。如果工作电压固定,则这两种方法只能提高电路的工作速度,并相应地增加了电路的功耗。在深亚微米工艺下,工作电压已经比较接近阈值电压,为了使工作电压有足够的下降空间,应该降低阔值电压;但是随着阈值电压的降低,亚阈值电流将呈指数增长,静态功耗迅速增加。因此,电压的下降空间有限。

4) 低功耗单元库

设计低功耗单元库是降低功耗的一个重要方法,包括调整单元尺寸、改进电路结构和版图设计。用户可以根据负载电容和电路延时的需要选择不同尺寸的电路来实现,这样会导致不同的功耗,因此可以根据需要设计不同尺寸的单元。同时,为常用的单元选择低功耗的实现结构,如触发器、锁存器和数据选择器等。

5) 低功耗状态机编码

状态机编码对信号的活动性具有重要影响,通过合理选择状态机状态的编码方法,减少状态切换时电路的翻转,可以降低状态机的功耗。其原则是:对于频繁切换的相邻状态,尽量采用相邻编码。例如:Gray码在任何两个连续的编码之间只有一位的数值不同,在设计计数器时,使用Gray码取代二进制码,则计数器的改变次数几乎减少一半,显著降低了功耗;在访问相邻的地址空间时,其跳变次数显著减少,有效地降低了总线功耗。

6) Cache的低功耗设计

作为现代微处理器中的重要部件,Cache的功耗约占整个芯片功耗的30%~60%,因此设计高性能、低功耗的Cach结构,对降低微处理器的功耗有明显作用。Cache低功耗设计的关键在于降低失效率,减少不必要的操作。通常用来降低Cache功耗的方法有以下两种:一种是从存储器的结构出发,设计低功耗的存储器,例如采用基于CAM的Cache结构;另一种是通过减少对Cache的访问次数来降低功耗。

以上主要是从硬件的角度来实现功耗的降低。除了硬件方法,通过软件方面的优化,也能显著地降低功耗。例如:在Crusoe处理器中,采用高效的超长指令(VLIW)、代码融合(Code Morphing)技术、LongRun电源管理技术和RunCooler工作温度自动调节等创新技术,获得了良好的低功耗效果。

IC卡的缺点是制造成本高。

《功率因数校正原理与控制IC及其应用设计》全面地介绍了功率因数校正(PFC)的类型、控制技术、工作原理和控制Ic及其应用与设计。《功率因数校正原理与控制IC及其应用设计》共分九章,主要内容包括功率因数与功率因数校正、功率因数校正的基本类型和控制技术及其工作原理、临界导电模式(CRM)PFC控制器、连续导电模式(ccM)平均电流控制PFc控制器、单级PF℃控制器、其他类型的PFC控制器、PFC与镇流器控制器组合IC、开关电源PFC与PWM控制器 组合1C及PFC功率模块等。对于各种PFlC控制IC的介绍,具体内容涉及其基本结构、引脚功能、性能特点、工作原理、典型应用电路与设计等。 《功率因数校正原理与控制IC及其应用设计》涵盖的内容广泛,资料翔实,插图丰富,技术新颖,具有系统性、实用性、指导性和前瞻性,并且深入浅出,通俗易懂。 《功率因数校正原理与控制IC及其应用设计》适合于电力与电子行业、电源行业和电光源行业从事研发和生产的工程技术人员阅读,并可供高等院校相关专业的师生参考。

- 相关百科

- 相关知识

- 相关专栏

- icoco厨柜

- iColor爱客装修

- ID+C室内设计与装修:法国设计师专辑

- id+c室内设计与装修

- ID室内装饰:主题住宅

- IGCC发电工程估算编制及项目划分导则

- IK

- IKEA 宜家的设计

- IKEA宜家家居攻略

- IKEABOOK宜家创意生活2

- IKEABOOK宜家创意生活3

- iLike就业:AutoCAD2010中文版多功能教材

- iLike就业3ds Max 2012中文版多功能教材

- iLike职场3ds Max 2011+VRay效果图制作完美实现

- iLike职场Photoshop CS4平面广告设计

- Illustrator 向量绘图实务(附光碟)

- 分形DGS单元结构设计及其在微带电路中的应用

- 逆变TIG焊机接触引弧电路的设计(引弧电路)

- 中国机械工程学会授予材料热处理工程师资格人员名单

- 以MSP430FW427为核心的远程数字水表设计

- 引江济淮工程淠河总干渠以北安徽段截污导流工程设计

- 中华大厦五层宏远公司办公室内装修工程施工组织设计

- 招远电视台制作播出系统数字化改造工程的设计与实践

- 全热回收地源热泵空调机组的系统及工程方案设计

- 展览馆装饰工程消防改造施工组织设计方案(91页)

- 支持群体设计的工程数据库管理系统的结构及实现

- 智能建筑工程设计中的机电设备集成配置系统总体设计

- 中国石化北京设计院标准工艺装置管道垫片选用规定

- 中航格澜阳光花园一期门禁对讲建设项目施工组织设计

- 在书香中沉睡——“川大河畔”高尚住宅小区景观设计

- 高效率PWM/PFM自动切换升压转换器的设计

- 智能小区以太接入交换机SNMP代理设计与实现