低功耗

随着计算机技术和微电子技术的迅速发展,嵌入式系统应用领域越来越广泛。节能是全球化的热潮,如计算机里的许多芯片过去用5V供电,现在用3.3V、1.8V,并提出了绿色系统的概念。很多厂商很注重微控制器的低功耗问题。电路与系统的低功耗设计一直都是电子工程技术人员设计时需要考虑的重要因素。

低功耗基本信息

| 中文名称 | 低功耗 | 外文名称 | low power consumption |

|---|

低功耗IC设计

微处理器的低功耗设计技术,首先必须了解它的功耗来源。其中时钟单元(Clock)功耗最高,因为时钟单元有时钟发生器、时钟驱动、时钟树和钟控单元的时钟负载;数据通路(Datapath)是仅次于时钟单元的部分,其功耗主要来自运算单元、总线和寄存器堆。除了上述两部分,还有存储单元(Memory),控制部分和输入/输出(Control,I/O)。存储单元的功耗与容量相关。

CMOS电路功耗主要由3部分组成:电路电容充放电引起的动态功耗,结反偏时漏电流引起的功耗和短路电流引起的功耗。其中,动态功耗是最主要的,占了总功耗的90%以上。

常用的低功耗设计技术

低功耗设计足一个复杂的综合性课题。就流程而言,包括功耗建模、评估以及优化等;就设计抽象层次而言,包括自系统级至版图级的所有抽象层次。同时,功耗优化与系统速度和面积等指标的优化密切相关,需要折中考虑。下面讨论常用的低功耗设计技术。

1) 动态电压调节

动态功耗与工作电压的平方成正比,功耗将随着工作电压的降低以二次方的速度降低,因此降低工作电压是降低功耗的有力措施。但是,仅仅降低工作电压会导致传播延迟加大,执行时间变长。然而,系统负载是随时间变化的,因此并不需要微处理器所有时刻都保持高性能。动态电压调节DVS(Dynarnic Voltage Scaling)技术降低功耗的主要思路是根据芯片工作状态改变功耗管理模式,从而在保证性能的基础上降低功耗。在不同模式下,工作电压可以进行调整。为了精确地控制DVS,需要采用电压调度模块来实时改变工作电压,电压调度模块通过分析当前和过去状态下系统工作情况的不同来预测电路的工作负荷。

2) 门控时钟和可变频率时钟

在微处理器中,很大一部分功耗来自时钟。时钟是惟一在所有时间都充放电的信号,而且很多情况下引起不必要的门的翻转,因此降低时钟的开关活动性将对降低整个系统的功耗产牛很大的影响。门控时钟包括门控逻辑模块时钟和门控寄存器时钟。门控逻辑模块时钟对时钟网络进行划分,如果在当前的时钟周期内,系统没有用到某些逻辑模块,则暂时切断这些模块的时钟信号,从而明显地降低开关功耗。采用"与"门实现的时钟控制电路。门控寄存器时钟的原理是当寄存器保持数据时,关闭寄存器时钟,以降低功耗。然而,门控时钟易引起毛刺,必须对信号的时序加以严格限制,并对其进行仔细的时序验证。

另一种常用的时钟技术就是可变频率时钟。它根据系统性能要求,配置适当的时钟频率以避免不必要的功耗。门控时钟实际上是可变频率时钟的一种极限情况(即只有零和最高频率两种值),因此,可变频率时钟比门控时钟技术更加有效,但需要系统内嵌时钟产生模块PLL,增加了设计复杂度。去年Intel公司推出的采用先进动态功耗控制技术的Montecito处理器,就利用了变频时钟系统。该芯片内嵌一个高精度数字电流表,利用封装上的微小电压降计算总电流;通过内嵌的一个32位微处理器来调整主频,达到64级动态功耗调整的目的,大大降低了功耗。

3) 并行结构与流水线技术

并行结构的原理是通过牺牲面积来降低功耗。将一个功能模块复制为n(n≥2)个相同的模块,这些模块并行计算后通过数据选择器选择输出,采用二分频的并行结构。

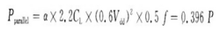

并行设计后,由于有多个模块同时工作,提高了吞吐能力,可以把每个模块的速度降低为原来的l/n。根据延时和工作电压的线性关系,工作电压可以相应降低为原来的l/n,电容增大为原来的n倍,工作频率降低为原来的l/n,根据式(1)功耗降低为原来的1/n2。并行设计的关键是算法设计,一般算法中并行计算的并行度往往比较低,并行度高的算法比较难开发。例如:若原模块的功耗为P=a×CL×V2dd×f,采用二分频结构,由于增加了一个模块和数据选择器,整个电容负载为2.2CL,工作频率为f/2,工作电压可以降为O.6 V,则其功耗为:

由此可见,二分频并行结构在保持原有电路性能的同时降低了60%的功耗。

流水线技术本质上也是一种并行。把某一功能模块分成n个阶段进行流水作业,每个阶段由一个子模块来完成,在子模块之间插入寄存器,如图5所示。若工作频率不变,对某个模块的速度要求仅为原来的1/n,则工作电压可以降低为原来的1/n,电容的变化不大(寄存器面积占的比例很小),功耗可降低为原来的1/n2,面积基本不变,但增加了控制的复杂度。例如,若原模块的功耗为P=α×C1×V2dd×f,采用流水线技术,由于增加了寄存器,整个电容负载为1.2CL,工作频率不变,工作电压降为0.6 V,则其功耗为

:

由此可见,流水线技术能显著降低系统功耗。

通过流水线技术和并行结构降低功耗的前提是电路工作电压可变。如果工作电压固定,则这两种方法只能提高电路的工作速度,并相应地增加了电路的功耗。在深亚微米工艺下,工作电压已经比较接近阈值电压,为了使工作电压有足够的下降空间,应该降低阔值电压;但是随着阈值电压的降低,亚阈值电流将呈指数增长,静态功耗迅速增加。因此,电压的下降空间有限。

4) 低功耗单元库

设计低功耗单元库是降低功耗的一个重要方法,包括调整单元尺寸、改进电路结构和版图设计。用户可以根据负载电容和电路延时的需要选择不同尺寸的电路来实现,这样会导致不同的功耗,因此可以根据需要设计不同尺寸的单元。同时,为常用的单元选择低功耗的实现结构,如触发器、锁存器和数据选择器等。

5) 低功耗状态机编码

状态机编码对信号的活动性具有重要影响,通过合理选择状态机状态的编码方法,减少状态切换时电路的翻转,可以降低状态机的功耗。其原则是:对于频繁切换的相邻状态,尽量采用相邻编码。例如:Gray码在任何两个连续的编码之间只有一位的数值不同,在设计计数器时,使用Gray码取代二进制码,则计数器的改变次数几乎减少一半,显著降低了功耗;在访问相邻的地址空间时,其跳变次数显著减少,有效地降低了总线功耗。

6) Cache的低功耗设计

作为现代微处理器中的重要部件,Cache的功耗约占整个芯片功耗的30%~60%,因此设计高性能、低功耗的Cach结构,对降低微处理器的功耗有明显作用。Cache低功耗设计的关键在于降低失效率,减少不必要的操作。通常用来降低Cache功耗的方法有以下两种:一种是从存储器的结构出发,设计低功耗的存储器,例如采用基于CAM的Cache结构;另一种是通过减少对Cache的访问次数来降低功耗。

以上主要是从硬件的角度来实现功耗的降低。除了硬件方法,通过软件方面的优化,也能显著地降低功耗。例如:在Crusoe处理器中,采用高效的超长指令(VLIW)、代码融合(Code Morphing)技术、LongRun电源管理技术和RunCooler工作温度自动调节等创新技术,获得了良好的低功耗效果。

低功耗造价信息

在嵌入式系统的设计中,低功耗设计(Low-Power Design)是许多设计人员必须面对的问题。

1)选用节能的微处理器 同样的工作状态,电源电压不同,功耗是非线性增加的。

我们是在CPU的性能(Performance)和功耗(Power Consumption)方面进行比较和选择。通常可以采用每执行1M次指令所消耗的能量来进行衡量,即Watt/MIPS。但是,这仅仅是一个参考指标,实际上各个CPU的体系结构相差很大,衡量性能的方式也不尽相同,所以,我们还应该进一步分析一些细节。 我们把CPU的功率消耗分为两大部分:内核消耗功率PCORE和外部接口控制器消耗功率PI/O,总的功率等于两者之和,即P=PCORE+PI /O。对于PCORE,关键在于其供电电压和时钟频率的高低;对于PI/O来讲,除了留意各个专门I/O控制器的功耗外,还必须关注地址和数据总线宽度。

2)尽量选用CMOS集成电路 CMOS集成电路(Complementary Metal Oxide Semiconductor)即互补金属-氧化物-半导体集成电路,它最大的优点是微功耗(静态功耗几乎为零),其次的优点是输出逻辑电平摆幅大,因而抗干扰能力强,同时它的工作温度范围也宽,因此CMOS电路一开始出现就和低功耗便携式仪器仪表结下了不解之缘。

3)、采用电池低电压供电 系统功耗和系统的供电电压存在着一定的函数关系。供电电压越高,系统功耗也就越大。目前已经出现了不少低电压供电(小于4.5V)的单片机及其外围电路,工作电压可低至1.8V。在1.8V~6V之间均可正常工作,而且对于测量精度没有影响。 在设计开发中要注意,单片机电源电压可以从6V降到1.8V,工作期间电压可以在该范围波动,但是国内的仿真器还达不到这个要求,一般都在5V下仿真工作。这时候的仿真和真正的工作状态是有区别的,所以单片机系统设计完之后一定要进行低电压测试,避免仿真时可以用,实际应用时出现问题。

4)、尽量使用"高速低频"工作方式 低功耗单片微机系统中几乎全部采用的是CMOS器件,而CMOS集成电路由自己的结构所决定,它静态功耗几乎为零,仅在逻辑状态发生转换期间,电路有电流流过。所以它的动态功耗和它的逻辑转换频率成正比,和电路的逻辑状态转换时间成正比。所以,CMOS集成电路从降低功耗的角度上来说应当快速转换,低频率地工作。

5)、充分利用微控制器上集成的功能 微控制器已经将许多硬件集成到一块芯片之中,使用这些功能比用扩展方式扩展外围电路要有效得多。首先单片化的成本要比使用扩展方式低,而且性能更好。如外围器件的驱动电压很难降低到微控制器芯片的水平,微控制器可以降低到1.8V,外围电路降到3V恐怕有相当多的芯片就会工作不稳定,而微控制器内部集成的硬件却可以有更好的电压适应能力。

6)、选用低功耗高效率的外围器件和电路 在必须选择使用某些外围器件时,尽可能选择低功耗、低电压、高效率的外围器件,象LCD液晶显示器、EEPROM等,这样是为了降低系统的总体功耗。此外还尽量选用低功耗及高效率的电路形式。低功耗的电路以低功耗为主要技术指标,它不盲目追求高速度和大的驱动能力,以满足要求为限度,因而电路的工作电流都比较小。

目前的低功耗设计主要从芯片设计和系统设计两个方面考虑。随着半导体工艺的飞速发展和芯片工作频率的提高,芯片的功耗迅速增加,而功耗增加又将导致芯片发热量的增大和可靠性的下降。因此,功耗已经成为深亚微米集成电路设计中的一个重要考虑因素。为了使产品更具竞争力,工业界对芯片设计的要求已从单纯追求高性能、小面积转为对性能、面积、功耗的综合要求。而微处理器作为数字系统的核心部件,其低功耗设计对降低整个系统的功耗具有重要的意义。

在嵌入式系统的设计中,低功耗设计(Low-Power Design)是许多设计人员必须面对的问题,其原因在于嵌入式系统被广泛应用于便携式和移动性较强的产品中去,而这些产品不是一直都有充足的电源供应,往往是靠电池来供电,所以设计人员从每一个细节来考虑降低功率消耗,从而尽可能地延长电池使用时间。事实上,从全局来考虑低功耗设计已经成为了一个越来越迫切的问题。

低功耗常见问题

-

低功耗贴片led灯价格是25元。 低功耗贴片led灯有超长寿命半导体芯片发光,无灯丝,无玻璃泡,不怕震动,不易破碎,使用寿命可达五万小时,光线健康光线中不含紫外线和红外线,不产生辐射,不含汞和氙等有害...

-

他的都好说,关键是无风扇要求比较麻烦···无风扇就得超低TDP···可是你既然是要看高清那么U的TDP要想太小也不可能···除非是配一台MODT。

-

低功耗霍尔开关的原理:1. 霍尔开关是一种利用霍尔效应的磁感应式电子开关,属于有源磁电转换器件。 2. 当一块通有电流的金属或半...

低功耗文献

低功耗CPU卡智能水表设计

低功耗CPU卡智能水表设计

低功耗CPU卡智能水表设计

低功耗设计足一个复杂的综合性课题,就流程而言,包括功耗建模、评估以及优化等;就设计抽象层次而言,包括自系统级至版图级的所有抽象层次。同时,功耗优化与系统速度和面积等指标的优化密切相关,需要折中考虑。

动态电压调节

动态功耗与工作电压的平方成正比,功耗可随着工作电压的降低以二次方的速度降低,因此降低工作电压是降低功耗的有力措施。但是,仅仅降低工作电压会导致传播延迟加大,执行时间变长。然而,系统负载是随时间变化的,因此并不需要微处理器所有时刻都保持高性能。动态电压调节DVS(Dynarnic Voltage Scaling)技术降低功耗的主要思路是根据芯片工作状态改变功耗管理模式,从而在保证性能的基础上降低功耗。在不同模式下,工作电压可以进行调整。为了精确地控制DVS,需要采用电压调度模块来实时改变工作电压,电压调度模块通过分析当前和过去状态下系统工作情况的不同来预测电路的工作负荷。

两种时钟

在微处理器中,很大一部分功耗来自时钟。时钟是惟一在所有时间都充放电的信号,而且很多情况下引起不必要的门的翻转,因此降低时钟的开关活动性可以对降低整个系统的功耗产生很大的影响。门控时钟包括门控逻辑模块时钟和门控寄存器时钟。门控逻辑模块时钟对时钟网络进行划分,如果在当前的时钟周期内,系统没有用到某些逻辑模块,则暂时切断这些模块的时钟信号,从而明显地降低开关功耗。门控寄存器时钟的原理是当寄存器保持数据时,关闭寄存器时钟,以降低功耗。然而,门控时钟易引起毛刺,必须对信号的时序加以严格限制,并对其进行仔细的时序验证。

另一种常用的时钟技术就是可变频率时钟。它根据系统性能要求,配置适当的时钟频率以避免不必要的功耗。门控时钟实际上是可变频率时钟的一种极限情况(即只有零和最高频率两种值),因此,可变频率时钟比门控时钟技术更加有效,但需要系统内嵌时钟产生模块PLL,增加了设计复杂度。Intel公司推出的采用先进动态功耗控制技术的Montecito处理器,就利用了变频时钟系统。该芯片内嵌一个高精度数字电流表,利用封装上的微小电压降计算总电流;通过内嵌的一个32位微处理器来调整主频,达到64级动态功耗调整的目的,大大降低了功耗。

两种技术

并行结构的原理是通过牺牲面积来降低功耗。将一个功能模块复制为n(n≥2)个相同的模块,这些模块并行计算后通过数据选择器选择输出,采用二分频的并行结构。

并行设计后,由于有多个模块同时工作,提高了吞吐能力,可以把每个模块的速度降低为原来的l/n。根据延时和工作电压的线性关系,工作电压可以相应降低为原来的l/n,电容增大为原来的n倍,工作频率降低为原来的l/n,根据式(1)功耗降低为原来的1/n2。并行设计的关键是算法设计,一般算法中并行计算的并行度往往比较低,并行度高的算法比较难开发。例如:若原模块的功耗为P=a×CL×V2dd×f,采用二分频结构,由于增加了一个模块和数据选择器,整个电容负载为2.2CL,工作频率为f/2,工作电压可以降为O.6 V。由此可见,二分频并行结构在保持原有电路性能的同时降低了60%的功耗。

流水线技术本质上也是一种并行。把某一功能模块分成n个阶段进行流水作业,每个阶段由一个子模块来完成,在子模块之间插入寄存器。若工作频率不变,对某个模块的速度要求仅为原来的1/n,则工作电压可以降低为原来的1/n,电容的变化不大(寄存器面积占的比例很小),功耗可降低为原来的1/n2,面积基本不变,但增加了控制的复杂度。例如,若原模块的功耗为P=α×C1×V2dd×f,采用流水线技术,由于增加了寄存器,整个电容负载为1.2CL,工作频率不变,工作电压降为0.6 V。由此可见,流水线技术能显著降低系统功耗。

通过流水线技术和并行结构降低功耗的前提是电路工作电压可变。如果工作电压固定,则这两种方法只能提高电路的工作速度,并相应地增加了电路的功耗。在深亚微米工艺下,工作电压已经比较接近阈值电压,为了使工作电压有足够的下降空间,应该降低阔值电压;但是随着阈值电压的降低,亚阈值电流可能呈指数增长,静态功耗迅速增加。因此,电压的下降空间有限。

低功耗单元库

设计低功耗单元库是降低功耗的一个重要方法,包括调整单元尺寸、改进电路结构和版图设计。用户可以根据负载电容和电路延时的需要选择不同尺寸的电路来实现,这样会导致不同的功耗,因此可以根据需要设计不同尺寸的单元。同时,为常用的单元选择低功耗的实现结构,如触发器、锁存器和数据选择器等。

状态机编码

状态机编码对信号的活动性具有重要影响,通过合理选择状态机状态的编码方法,减少状态切换时电路的翻转,可以降低状态机的功耗。其原则是:对于频繁切换的相邻状态,尽量采用相邻编码。例如:Gray码在任何两个连续的编码之间只有一位的数值不同,在设计计数器时,使用Gray码取代二进制码,则计数器的改变次数几乎减少一半,显著降低了功耗;在访问相邻的地址空间时,其跳变次数显著减少,有效地降低了总线功耗。

低功耗设计

作为现代微处理器中的重要部件,Cache的功耗约占整个芯片功耗的30%~60%,因此设计高性能、低功耗的Cach结构,对降低微处理器的功耗有明显作用。Cache低功耗设计的关键在于降低失效率,减少不必要的操作。通常用来降低Cache功耗的方法有以下两种:一种是从存储器的结构出发,设计低功耗的存储器,例如采用基于CAM的Cache结构;另一种是通过减少对Cache的访问次数来降低功耗。

以上主要是从硬件的角度来实现功耗的降低。除了硬件方法,通过软件方面的优化,也能显著地降低功耗。例如:在Crusoe处理器中,采用高效的超长指令(VLIW)、代码融合(Code Morphing)技术、LongRun电源管理技术和RunCooler工作温度自动调节等创新技术,获得了良好的低功耗效果。

低功耗RTU集数据采集、传输、存储功能于一体,采用低功耗设计,特别适用于太阳能供电的监测现场,可大大减少太阳能供电成本并降低施工难度,广泛应用于气象、水文水利、地质等行业。

功耗是微处理器设计长期面临的问题,分析当前的研究状况,未来的低功耗微处理器设计研究有如下发展趋势:

首先,系统级的低功耗设计研究。抽象层次越高,采用低功耗技术功耗可降低的比例越大。

其次,面向功耗的软硬件协同设计。而向功耗的软硬件协同设计可以获得功耗优化的系统架构,再配合有效的功耗管理,可以大大降低最终的功耗。

再次,异步电路的研究。同步电路的时钟功耗在整个系统的功耗中占了相当大的比例。异步逻辑无需全局时钟,而是采用握手信号协调模块问的工作,减少了时钟驱动和同步电路中很多不必要的翻转,从而有效地降低了功耗。然而,异步电路实现困难,且缺乏EDA软件的支持,因而还有待于进一步的研究。

- 相关百科

- 相关知识

- 相关专栏

- 磁座钻

- 西亚特Leon

- 极上雅境

- 新型塑料挤出机头设计

- 皮带运输机通廊建筑构造

- 钣金展开技术手册

- 工业自动化设备

- 软轴

- 低可侦测性

- 半导体技术

- 胎头低横位

- 水冷机

- 广州市环境噪声污染防治规定

- Nokia x500

- 圣宝SV-507途乐

- 工程爆破技术

- 无线传感网射频芯片中4.8GHz低功耗压控振荡器设计

- MSP430单片机的低功耗电流互感器高压端的实现

- PIC16F873A单片机的温控阀门的低功耗设计

- MSP430的分界负荷开关低功耗控制系统设计

- TI针对便携式高精度应用推出低功耗零漂移仪表放大器

- TGS8100最小尺寸低功耗空气质量VOC传感器

- 低压差低功耗稳压IC

- 智能平台推出面向超低功耗应用的新单板计算机

- PIC单片机在电话远程控制器中的低功耗设计

- 兼容SPARCV8结构的FPC及其低功耗设计

- gshare分支预测器低功耗设计方法

- MSP430F412的低功耗空调温度控制器

- PIC16F688的翻斗式雨量计低功耗设计

- GPRS的无线水表监控系统的低功耗设计

- PIC单片机的低功耗无磁IC卡水表设计

- SoC的低成本低功耗同轴电缆三网融合系统