JTAG接口

JTAG(Joint Test Action Group;联合测试工作组)是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

JTAG接口基本信息

| 中文名称 | JTAG接口 | 外文名称 | Joint Test Action Group |

|---|---|---|---|

| 用途 | 芯片内部测试 | 接口 | TMS、TCK、TDI、TDO |

通常所说的JTAG大致分两类,一类用于测试芯片的电气特性,检测芯片是否有问题;一类用于Debug,一般支持JTAG的CPU内都包含了这两个模块。

一个含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器和挂在CPU总线上的设备,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)内置模块的寄存器,像UART,Timers,GPIO等等的寄存器。

上面说的只是JTAG接口所具备的能力,要使用这些功能,还需要软件的配合,具体实现的功能则由具体的软件决定。

例如下载程序到RAM功能。了解SOC的都知道,要使用外接的RAM,需要参照SOC DataSheet的寄存器说明,设置RAM的基地址,总线宽度,访问速度等等。有的SOC则还需要Remap,才能正常工作。运行Firmware时,这些设置由Firmware的初始化程序完成。但如果使用JTAG接口,相关的寄存器可能还处在上电值,甚至是错误值,RAM不能正常工作,所以下载必然要失败。要正常使用,先要想办法设置RAM。在ADW中,可以在Console窗口通过Let 命令设置,在AXD中可以在Console窗口通过Set命令设置。

JTAG接口造价信息

JTAG(Joint Test Action Group ,联合测试行动小组 ) 是一种国际标准测试协议,主要用于芯片内部测试及对系统进行仿真、调试, JTAG 技术是一种嵌入式调试技术,它在芯片内部封装了专门的测试电路 TAP ( Test Access Port ,测试访问口),通过专用的 JTAG 测试工具对内部节点进行测试。

如今大多数比较复杂的器件都支持 JTAG 协议,如 ARM 、 DSP 、 FPGA 器件等。标准的 JTAG 接口是 4 线: TMS 、 TCK 、 TDI 、 TDO ,分别为测试模式选择、测试时钟、测试数据输入和测试数据输出。如今 JTAG 接口的连接有两种标准,即 14 针接口和 20 针接口,其定义分别如下所示。

14针JTAG接口

1 、 13 VCC 接电源

2 、 4 、 6 、 8 、 10 、 14 GND 接地

3 nTRST 测试系统复位信号

5 TDI 测试数据串行输入

7 TMS 测试模式选择

9 TCK 测试时钟

11 TDO 测试数据串行输出

12 NC 未连接

20针JTAG接口

1 VTref 目标板参考电压,接电源

2 VCC 接电源

3 nTRST 测试系统复位信号

4、6、8、10、12、14、16、18、20 GND 接地

5 TDI 测试数据串行输入

7 TMS 测试模式选择

9 TCK 测试时钟

11 RTCK 测试时钟返回信号

13 TDO 测试数据串行输出

15 nRESET 目标系统复位信号

17 、 19 NC 未连接

10针JTAG接口

仿真器端口 AVR端口 备注

1. TCK TCK

2. NC NC

3. TDO TDO

4. Vtref VCC

5. TMS TMS

6. nSRST RESET

7. NC / Vsupply NC / VCC JTAG ICE仿真器:VCC;JTAG ICE mkII仿真器:NC

8. nTRST NC ATMEL尚且保留该端口,如今暂不使用它,未来可能会使用

9. TDI TDI

10.GND GND

JTAG最初是用来对芯片进行测试的,JTAG的基本原理是在器件内部定义一个TAP(Test Access Port;测试访问口)通过专用的JTAG测试工具对内部节点进行测试。JTAG测试允许多个器件通过JTAG接口串联在一起,形成一个JTAG链,能实现对各个器件分别测试。如今,JTAG接口还常用于实现ISP(In-System Programmer,在系统编程),对FLASH等器件进行编程。

JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程然后再装到板上,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。JTAG接口可对DSP芯片内部的所有部件进行编程。

JTAG引脚定义

具有JTAG口的芯片都有如下JTAG引脚定义:

TCK--测试时钟输入;

TDI--测试数据输入,数据通过TDI输入JTAG口;

TDO--测试数据输出,数据通过TDO从JTAG口输出;

TMS--测试模式选择,TMS用来设置JTAG口处于某种特定的测试模式。

可选引脚TRST--测试复位,输入引脚,低电平有效。

含有JTAG口的芯片种类较多,如CPU、DSP、CPLD等。

JTAG内部有一个状态机,称为TAP控制器。TAP控制器的状态机通过TCK和TMS进行状态的改变,实现数据和指令的输入。

JTAG芯片的边界扫描寄存器

JTAG标准定义了一个串行的移位寄存器。寄存器的每一个单元分配给IC芯片的相应引脚,每一个独立的单元称为BSC(Boundary-Scan Cell)边界扫描单元。这个串联的BSC在IC内部构成JTAG回路,所有的BSR(Boundary-Scan Register)边界扫描寄存器通过JTAG测试激活,平时这些引脚保持正常的IC功能。

JTAG在线写Flash的硬件电路设计

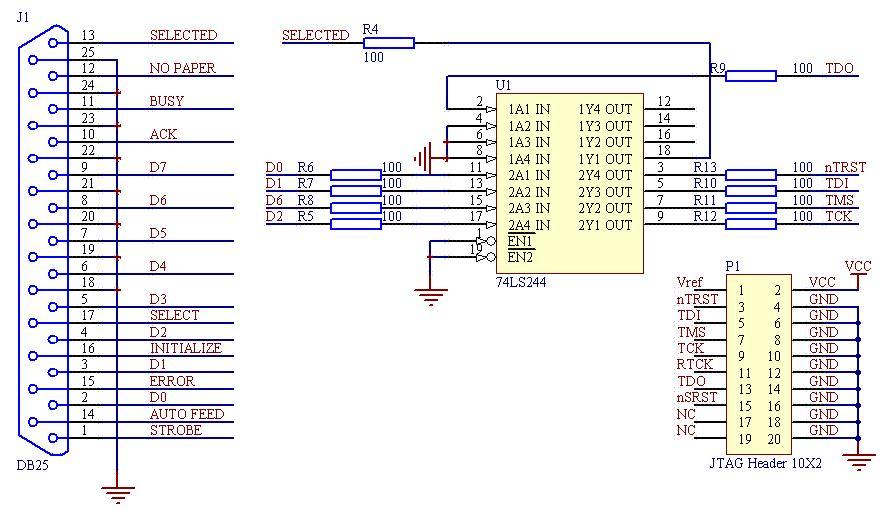

JTAG在线写Flash的硬件电路设计和与PC的连接方式

以含JTAG接口的StrongARM SA1110为例,Flash为Intel 28F128J32 16MB容量。SA1110的JTAG的TCK、TDI、TMS、TDO分别接PC并口的2、3、4、11线上,通过程序将对JTAG口的控制指令和目标代码从PC的并口写入JTAG的BSR中。在设计PCB时,必须将SA1110的数据线和地址线及控制线与Flash的地线、数据线和控制线相连。因SA1110的数据线、地址线及控制线的引脚上都有其相应BSC,只要用JTAG指令将数据、地址及控制信号送到其BSC中,就可通过BSC对应的引脚将信号送给Flash,实现对Flash的操作。JTAG的系统板设计和连线关系如图3所示。

使用TAP状态机的指令实行对Flash的操作

通过TCK、TMS的设置,可将JTAG设置为接收指令或数据状态。JTAG常用指令如下:

SAMPLE/PRELOAD--用此指令采样BSC内容或将数据写入BSC单元;

EXTEST--当执行此指令时,BSC的内容通过引脚送到其连接的相应芯片的引脚,我们就是通过这种指令实现在线写Flash的;

BYPASS--此指令将一个一位寄存器置于BSC的移位回路中,即仅有一个一位寄存器处于TDI和TDO之间。

在PCB电路设计好后,即可用程序先将对JTAG的控制指令,通过TDI送入JTAG控制器的指令寄存器中。再通过TDI将要写Flash的地址、数据及控制线信号入BSR中,并将数据锁存到BSC中,用EXTEST指令通过BSC将写入Flash。

软件编程

在线写Flash的程序用Turbo C编写。程序使用PC的并行口,将程序通过含有JTAG的芯片写入Flash芯片。程序先对PC的并口初始化,对JTAG口复位和测试,并读Flash,判断是否加锁。如加锁,必须先解锁,方可进行操作。写Flash之前,必须对其先擦除。将JTAG芯片设置在EXTEST模式,通过PC的并口,将目标文件通过JTAG写入Flash,并在烧写完成后进行校验。程序主流程如图4所示。

通过JTAG的读芯片ID子程序如下:

电路设计和编程中的注意事项

①Flash芯片的WE、CE、OE等控制线必须与SA1110的BSR相连。只有这样,才能通过BSR控制Flash的相应引脚。

②JTAG口与PC并口的连接线要尽量短,原则上不大于15cm。

③Flash在擦写和编程时所需的工作电流较大,在选用系统的供电芯片时,必须加以考虑。

④为提高对Flash的编程速度,尽量使TCK不低于6MHz,可编写烧写Flash程序时实现。

JTAG接口常见问题

-

public class LinkedList extends AbstractSequentialList implements List, Queue, ...

-

一般系统默认是SATA做主盘的 而且SATA没跳线设置! 主要的在主版COMS里面设置看看了!回答者:3683680 - 秀才 二级 8-20 17:08SATA硬盘BIOS设置图解分类:默认栏目 由...

-

预留线材,根据您当地计算规则里不同种类的不同预留长度计算

JTAG接口文献

Zhaga于近日发布LED射灯模块接口规范Book2

Zhaga于近日发布LED射灯模块接口规范Book2

近日,国际Zhaga联盟发布了圆柱形、嵌入式LED射灯接口规范Book2,为供应商提供SSL灯具设计可互操作的模块化方法。Zhaga接13规范Book2定义了固态照明(SSL)模块主要用于筒灯应用程序接口的规范,并创建了一个认证产品数据库(市面有售)。

EmJTAG协议转换器的设计与实现

EmJTAG协议转换器的设计与实现

协议转换器是ARM嵌入式系统调试技术的关键所在。本文介绍了一种基于USB接口的协议转换器(EmJTAG)设计思想,并给出了硬件设计和固件设计的实现方法。

SBW是MSP430的调试接口的一种。

- 外文名

- SBW

- 类别

- MSP430的调试接口

SBW接口

SBW功能与JTAG功能一样,但只需两根线(1根信号线,1根复位线)即可完成JTAG接口的所有功能。主要用SBWTCK(连接到JTAG仿真器的7脚TCK)与SBWTDIO(连接到JTAG仿真器的1脚TDO/TDI)。SBW(Spy-Bi-Wire,双面间谍),该接口主要用于小于28脚的2系列的430单片机,因为28脚以内的2系列单片机的JTAG接口一般与IO口复用,为了给用户预留更多的IO口,才推出了SBW接口。同样SBW接口可以用于仿真器及编程器。只有2xx系列和5xx系列的单片机带有SBW接口。 2100433B

书名单板级JTAG测试技术

书号978-7-118-09986-7

作者王承、刘治国

出版时间2015年6月

译者

版次1版1次

开本32

装帧平装

出版基金

页数205

字数190

中图分类TN407

丛书名

定价58.00

第1章测试的基本概念1

1.1数字电路测试1

1.1.1测试1

1.1.2测试分类2

1.1.3数字电路分类2

1.2故障及故障模型3

1.3算法3

1.4测试覆盖率和故障检出率4

1.5测试矢量4

1.5.1组合电路的测试矢量生成6

1.5.2时序电路的测试矢量生成10

1.6可测性15

1.6.1可控性15

1.6.2可观性16

1.6.3可测性设计方法17

第2章单板级JTAG测试31

2.1背景介绍31

2.2传统单板测试方法的困难32

2.2.1在线测试33

2.2.2光学测试33

2.2.3功能测试34

2.3生产制造应用35

2.4JTAG测试技术36

2.5单板级JTAG测试38

2.6JTAG测试的优缺点39

第3章IEEE1149.X标准40

3.1IEEE1149.1(边界扫描测试)40

3.1.1边界扫描测试概述40

3.1.2边界扫描硬件结构42

3.1.3边界扫描描述语言69

3.2IEEE1532(在系统编程)84

3.2.1标准测试与编程语言85

3.2.2在系统配置硬件结构87

3.2.3数据和地址寄存器的访问89

3.2.4在系统配置指令89

3.2.5在系统编程实现91

3.3IEEE1149.6(高级数字网络边界扫描测试)93

3.3.1连接模型93

3.3.2IEEE1149.6架构95

3.3.3IEEE1149.6指令96

3.3.4IEEE1149.6应用实例99

第4章单板级边界扫描可测性设计100

4.1测试点和测试探针100

4.2应力分析102

4.3菊花链103

4.4复位管脚设置104

4.5菊花链TAP端口设置104

4.6不同电压芯片的连接106

4.7优选遵循IEEE1149.1芯片108

4.8配置管脚设置108

4.9扫描链中芯片个数108

4.10逻辑芯片的设置110

4.11存储器的连接110

4.12器件族的连接111

4.13其他情况111

4.14测试点的设计111

4.15小结113

第5章边界扫描测试技术应用116

5.1故障模型116

5.2器件模型117

5.2.1关键字符118

5.2.2器件模型实例118

5.3测试算法130

5.3.1计数/补偿算法130

5.3.2走步算法131

5.3.3边界扫描测试流程132

5.4芯片级测试134

5.4.1JTAG总线测试134

5.4.2芯片寄存器测试135

5.5单板级测试139

5.5.1基础测试139

5.5.2上/下拉测试141

5.5.3互连测试142

5.5.4器件族测试143

5.5.5存储器测试144

5.6系统级测试145

5.6.1系统级测试结构146

5.6.2多点网关芯片147

5.6.3基于STA112的系统级测试架构149

5.7应用方式150

5.8优缺点分析150

第6章串行矢量格式152

6.1引言152

6.2SVF命令集152

6.2.1SVF文件152

6.2.2SVF命令集153

6.3SVF命令详述154

6.3.1寄存器测试结束155

6.3.2测试频率设置155

6.3.3寄存器头设置156

6.3.4并行测试矢量设置158

6.3.5并行管脚映射159

6.3.6测试运行设置160

6.3.7寄存器扫描163

6.3.8状态路径设置165

- 相关百科

- 相关知识

- 相关专栏

- 微槽群复合相变冷却技术

- 磁化增氧水龙头

- 红外线自动水龙头

- 即热式电热水龙头

- 野枇杷叶

- 天津木雕

- 数显压力表

- 陶瓷结合剂金刚石砂轮

- 虫草蜜炼川贝枇杷膏

- 电热水龙头温度保险丝

- 龙头式净水器

- 自闭式水龙头

- 喷雾式节能水嘴

- 节能水嘴

- 龙门式三坐标测量仪

- 枇杷栽培技术

- 智能建筑虚拟仪器监控系统与控制网络的接口技术

- 在地铁建设、运营中屏蔽门系统与相关专业的接口分析

- 一拖多变频空调产品测试系统与室外机通信接口

- 在磁翻板液位计安装时为什么要在法兰接口处加装阀门

- 光纤接口总结大全(FCSTSCGBICSFPLC)

- 基于PDIUSBD12无线USB接口收发器设计

- 基于C语言51系列单片机专用测试设备校准接口设计

- 基于SOPCGPIB-UART接口协议转换器设计

- 夯管钢管接口连接分项工程(验收批)质量验收记录表

- 基于RS232接口环境试验设备自动测试系统设计

- 基于白盒测试ParlayAPI接口测试方法设计

- 基于Wolfson音频SoCI~2C总线接口设计

- 基于CK-Core处理器SDIO接口主控制器设计

- 关于施工企业物资管理信息系统模块化及开放接口设计

- 基于ISP器件ISD系列SPI串口通信接口设计

- 基于DSP和FPGA油田测井系统总线通信接口设计