- 首页 >

- > 74hc138译码器

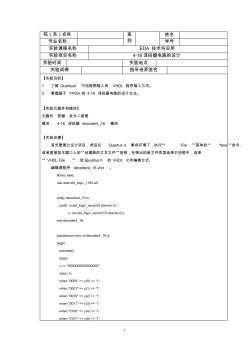

1 院(系)名称 班 别 姓名 专业名称 学号 实验课程名称 EDA 技术与应用 实验项目名称 4-16译码器电路的设计 实验时间 实验地点 实验成绩 指导老师签名 【实验目的】 1. 了解 QuartusII 中电路图输入和 VHDL 程序输入方式。 2. 掌握基于 FPGA 的 4-16 译码器电路的设计方法。 【实验元器件和模块】 元器件:按键、发光二极管 模块: 4-16 译码器 decoder4_16 模块 【实验步骤】 首先要建立设计项目,然后在 Quartus II 集成环境下,执行“ File ”菜单的“ New”命令, 或者直接按主窗口上的“创建新的文本文件”按钮,在弹出的新文件类型选择对话框中,选择 “ VHDL File ”,进入Quartus II 的 VHDL 文本编辑方式。 编辑源程序 decoder4_16.vhd 。 library ieee; use

大作业 3---- 4-16译码器的设计 一、功能表 EN X[4] X[3] X[2] X[1] Y[16] 1 d d d d 0000000000000000 0 0 0 0 0 0000000000000001 0 0 0 0 1 0000000000000010 0 0 0 1 0 0000000000000100 0 0 0 1 1 0000000000001000 0 0 1 0 0 0000000000010000 0 0 1 0 1 0000000000100000 0 0 1 1 0 0000000001000000 0 0 1 1 1 0000000010000000 0 1 0 0 0 0000000100000000 0 1 0 0 1 0000001000000000 0 1 0 1 0 0000010000000000 0 1 0 1

热门知识

74hc138译码器-

话题: 工程造价kei19820505

精华知识

74hc138译码器-

话题: 地产家居wujinkeiqiu

-

话题: 地产家居eminem1990

最新知识

74hc138译码器-

话题: 工程造价zx87971562

-

话题: 建筑设计songkaisong

74hc138译码器知识来自于造价通云知平台上百万用户的经验与心得交流。 注册登录 造价通即可以了解到相关74hc138译码器最新的精华知识、热门知识、相关问答、行业资讯及精品资料下载。同时,造价通还为您提供材价查询、测算、询价、云造价等建设行业领域优质服务。手机版访问:74hc138译码器

- 12YJ8第74页的室外钢梯

- 12YJ8第74页的钢梯计算过程

- 12YJ8第74页的钢梯重量

- 12YJ8第74页钢梯的计算

- 非公开招标74号令

- 财政部非公开招标74号

- 公开招标74号

- 招标采购74号文

- 政府非招标采购74

- 政府采购非招标74号

- Macha译码器的技术改造及检修程序的开发

- EDA4-16译码器电路设计

- 基于压电堆驱动器的喷嘴挡板式气体控制阀

- 电气工程及其自动化特色专业建设探索

- 分形DGS单元结构设计及其在微带电路中的应用

- 磷铵技术改造五大磷肥工程的建议

- 以大豆油多元醇制备的硬质聚氨酯泡沫塑料的性能

- 逆变TIG焊机接触引弧电路的设计(引弧电路)

- 预制砌块(砖、石)挡土墙工程砌体施工安全技术交底

- 应用模糊数学理论对公路工程建设项目方案的综合评价

- 引嫩工程扩建区土壤水盐动态与防治土壤盐碱措施

- 中华华丹雨、污水管道沟槽开挖专项施工方案教学教材

- 中国工程图学学会成立工程与制造系统集成化分会

- 中国吹制玻璃行业市场前景分析预测年度报告(目录)

- 可替代现有隔热保温材料的新型材料

- 医院病房楼工程施工装饰装修工程施工控制

- 在生活中构筑自然——河南天旺园林工程有限公司剪影